Betriebsdokumentation Heft 1

Personal computer EC 1834

3., überarbeitete Auflage Karl-Marx-Stadt 1989 Betriebsdokumentation.

#### Inhalt

- I. Technische Beschreibung

- II. Betriebsanleitung (siehe Software Dokumentation "Anleitung für den Bediener")

- III. Wartungsvorschrift

- IV. Aufstell- und Inbetriebnahmevorschrift (siehe Software Dokumentation "Anleitung für den Bediener")

- V. Lebenslaufakte (siehe Werksattest)

- · VI. Verzeichnis der Ersatzteile, Werkzeuge und Zubehörteile

1.62.540117.8 (GER) 085-3-000 850.53.01.001

#### I. Technische Beschreibung

#### Inhaltsverzeichnis

- 1. Einleitung

- 2. Anwendungsbereich

- 3. Technische Parameter

- 4. Bestandteile des Erzeugnisses

- 5. Aufbau und Arbeitsweise des Erzeugnisses

- 5.1. Aufbau

- 5.2. Arbeitsweise

- Aufbau und Arbeitsweise der Bestandteile des Erzeugnisses (siehe "Technische Beschreibung" der Baugruppen)

- 7. Mess-, Steuerungs- und Regelungseinrichtungen

- 8. Werkzeuge und Zubehör

- 9. Aufstellung und Montage

- 10. Kennzeichnung und Plombierung

- 11. Masse und Art der Verpackung

#### 1. Einleitung

Die vorliegende Dokumentation dient in erster Linie zur Unterstützung der Qualifikation von Servicetechnikern für den PC EC 1834.

Gemäss der einheitlichen Kundendienstkonzeption des Kombinats Robotron soll der Servicetechniker befähigt werden, neue Geräte zu installieren und erforderliche Einstellungen vorzunehmen sowie Störungen am PC beim Anwender zu erkennen, die fehlerhafte Baugruppe zu orten und auszutauschen. Er wendet zur Fehlersuche hauptsächlich die bereitgestellte Diagnosesoftware an. Dazu ist es erforderlich, dass der Servicetechniker neben dem technischen Wissen auch Grundkenntnisse in der Bedienung der Hardware, der Arbeit mit den Dienst- und Hilfsprogrammen und einen Überblick Über Betriebssystem sowie Standardsoftware besitzt. Mit dem Erzeugnis "Personalcomputer EC 1834 " beginnt der VEB Kombinat Robotron eine mit den RGW-Staaten abgestimmte Entwick-

lungslinie hochleistungsfähiger Arbeitsplatztechnik.

### 2. Anwendungsbereich

Das Gerät EC 1834 gehört zur 2. Generation der Personalcomputer. Seine "Voläufererzeugnisse BC A 5120/A 5130 und PC 1715 erreichen nicht annähernd seine Leistungsfähigkeit. Eine qualitativ bessere Hardware-Basis gestattet eine Reihe von Anwendungen, die erst mit dem Einsatz dieses PC realisiert werden kann.

Der PC EC 1834 ist kompatibel zum PC/XT und analogen Geräten. Durch das Betriebssystem DCP 3.20 (seit 10/88 DCP 3.30) wird die notwendige Vorbereitungs- und Programmierzeit wesentlich verkürzt. Umfangreiche Menüauswahl und Hilfstexte unterstützen die Kommunikation zwischen Bediener, Programmierer und Gerät. Für die Aussattungsvariante Farbbildschirm sind wichtige Texte besonders und in Farbe hervorgehoben. Der Computer wird in verschiedenen Grundkonfigurationen angeboten. Eingesetzt wird das Gerät als Sologerät und als Terminal. Beides, Gerät und Betriebssystem sind als offene Systeme konzipiert. Die Peripherie kann beliebig erweitert werden.

Zu den Einsatzgebieten gehören u.a.:

- CAD-Anwendungen

- Softwareentwicklungen

- Betriebswirtschaftliche Aufgaben

- Wissentschaftlich-technische Aufgaben

Als 2. Betriebssystem steht ab Mitte 1989 MUTOS zur Verfügung.

#### 3. Technische Parameter

Netzspannung: 220 V (187...242 V)

Netzfrequenz: 47...63 Hz

Umgebungsbedingungen : Einsatzklasse 2 nach TGL 26465

Temperatur +10 bis +35  $^{\text{c}}$  \( \text{C} \) max. Temperaturgradient 15 K/h max. rel Luftfeuchte 80% bei 25  $^{\text{c}}$  \( \text{C} \) Luftdruck 84...107 kPa

Funkentstörung: entsprechend TGL 20885/12 F1,F3

sowie nach VDE 8718 und GOST 23511/79

Schutzgrad :

IP 20 nach TGL RGW 778 für das Netzteil der Systemeinheit und für die Monitore IP 00 für alle übrigen Funktionsgruppen

Schutzklasse :

Schalleistungspegel:

1 nach TGL 21366 Leerlauf max. 52 dB AS Betrieb max, 65 dB AS

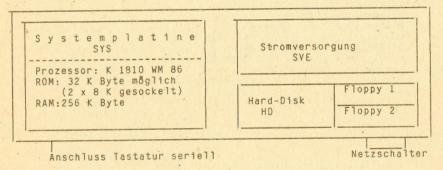

Technische Daten der Systemeinheit

Kombinierte Plast-Blech-Konstruktion bestehend aus Gefäss :

- Bodenwanne und Deckel aus Blech, der Deckel ist ohne

Werkzeug einfach zu öffnen

- Rückwand und Vorderwand aus Plast - Aufnahme für die Datenträgerlaufwerke - Netzschalteinrichtung und Anzeigeelemente

(SVE) mit Lüfter: Das Netzteil ist voll verkleidet und realisiert intern alle Schutzgüteforderungen bezüglich elektrischer Sicherheit.

Abmessungen (mm) :

Breite 517

Tiefe 406

Höhe 140

Masse :

16 bis 20 kg je nach Ausstattung

Leistungsaufnahme:

max. 150 W

Kühlung :

zwangsbelüftet, Luftaustritt nach hinten

Netzschalter:

integrierter Bestandteil des Netzteiles. über Gestänge von vorn bedienbar

Anzeigefunktionen :

Betriebsanzeige (LED)

Harddisk-Funktionsanzeige (LED)

akustischer Signalgeber (programmierbar)

Erweiterungssteckplätze: 8 Plätze für BLP in den Abmessungen 100 mm x 360/300/240/172,5 mm

Aufnahmerahmen für Datenträgerlaufwerke :

1 x Harddisk-Laufwerk 2 x 5,25 Zoll Floppy-Disk-Laufwerk oder 4 x 5,25 Zoll Floppy-Disk-Laufwerk

Hinweis : Die technischen Daten der einzelnen Funktionsgruppen sind dem jeweiligen Kapitel der Technischen Beschreibung zu entnehmen.

#### 4. Bestandteile des Erzeugnisses

Grundlage der Hardware ist das sowjetische Mikrorechnersystem K 1810 auf der Basis des 16-bit Mikroprozessors K 1810 WM 86. Der interne Hauptspeicher (RAM) hat eine Kapazität von 256 KByte und kann wahlweise auf bis zu 640 KByte erweitert werden. In der Systemeinheit befindet sich die gesamte Elektronik auf der waagerecht liegenden Systemplatine mit, je nach Ausstattung, bis zu acht senkrecht angeordneten, steckbaren Adaptern u.a. für

- Speichererweiterung

- monochromatischen alphanumerischen Bildschirm

- Farh/Grafik-Bildschirm

- Floppy-Disk

- Hard-Disk

- Netzwerk-Anschluss

- Anschluss V.24/IFSS

- Drucker

Der PC kann mit ein, zwei oder vier 5.25"-Folienspeicherlaufwerken robotron K 5601 ausgerüstet sein. Bei den Varianten mit weniger als vier Laufwerken kann wahlweise zusätzlich ein Harddisk installiert werden.

Grundsätzlich wird für den Anschluss des Hauptdruckers ein Centronics- Interface zur Verfügung gestellt. Zwei oder vier Interfaces V24 bzw IFSS gewährleisten den Anschluss zusätzlicher Peripherie wie Zweitdrucker, Plotter, Digitalisiergerät sowie spezielle Messgeräte.

Die Kommunikation mit dem Computer erfolgt über monochromatischen alphanumerischen bzw. grafikfähigen oder Color/Grafik-Bildschirm und über eine Flachtastatur.

### 5. Aufbau und Arbeitsweise des Erzeugnisses

#### 5.1. Aufbau

#### Erweiterungsmöglichkeiten:

| 1   | Speichererweiterung um 384 K Byte                       | SE      |  |

|-----|---------------------------------------------------------|---------|--|

| 1.  | Monochromatischer alphanumerischer Bildschirmadapter    | ABA     |  |

| 2.  | Farb/Grafik-Bildschirmadapter ( belegt zwei Steckplätze | )· FBA  |  |

| 3.  | Hard-Disk-Controller                                    | HDC     |  |

| 4.  | Floppy-Disk-Controller                                  | FDC     |  |

| 5.  | Adapter für serielle Kommunikation                      | ASC/ASK |  |

| 0.  | Druckeradapter (Centronics)                             | DA      |  |

|     |                                                         | BUS     |  |

|     | Busverlängerung                                         | KIF     |  |

|     | KIF-Adapter                                             | LAN     |  |

| 10. | LAN-Adapter                                             |         |  |

Zur Nutzung der international angebotenen Adapterplatten mit direktem Steckverbinder wird auch eine Austattungsvariante in folgender Aufstellung angeboten:

2 Steckplätze mit direktem Steckverbinder 5 Steckplätze mit indirektem Steckverbinder.

#### 5.2. Arbeitsweise

#### 5.2.1. Betriebssystem

Das Standardbetriebssystem des PC 1834 ist das Betriebssystem DCP 3.20 (DCP = Disk Control Program). Es ist kompatibel zu den entsprechenden PC-DOS-Versionen (DOS = Disk Operating System). Der Kern des Betriebssystems besteht aus den Komponenten

ROM-BIOS, der u.a. die physischen Gerätetreiber, Testroutinen und die BOOT-Routine enthält;

BIO.COM, die logischen Gerätetreiber;

DOS.COM, das logische System des Kerns und die Programmier-Systemschnittstelle:

COMMAND.COM, dem Kommandointerpreter.

Kommunikation mit dem Betriebssystem DCP 3.20 erfolgt den Kommandointerpreter COMMAND.COM, mit dessen Hilfe auf eine Vielzahl von Kommandos zugegriffen werden kann. Externe Kommandos befinden sich auf Diskette oder Festplatte, interne Kommandos beinhaltet der Interpreter selbst.

Interne Kommandos realisieren u.a. das

- Kopieren von Dateien

- Anlegen von Verzeichnissen

- Andern des aktuellen Verzeichnisses

- Auslisten von Verzeichnissen

- Löschen von Dateien und Verzeichnissen

- Umbenennen von Verzeichnissen

- Definieren von Suchpfaden ausführbarer Dateien

- Auslisten von Dateien sowie

- Anzeige und Ausgabe von Datum und Uhrzeit

über externe Kommandos können z. B. folgende Funktionen aufgerufen werden:

- Formatieren von Diskette oder Festplatte

- Vergleichen von zwei Dateien - Vergleich von zwei Disketten

- Kopieren einer Diskette auf eine andere

- Sichern von Dateien auf Disketten

- Durchsuchen von Dateien nach Zeichenketten

- Anzeige aller Verzeichnispfade und Auflistung der Dateien der Unterverzeichnisse

- Druck des Inhaltes eines Farb/Grafik-Bildschirmes

- Modus - Festlegung für Drucker, Bildschirm oder asynchrone Datenübertragung

- Ausgabe von Dateien auf Drucker

- Einstellung der Tastatur-Ländervariante

- Auswahl des Tastaturtyps und des Datum-/Zeitformates

- Kopieren des DCP auf ein anderes Laufwerk

- Konvertieren von SCPX-Dateien

### 5.2.2. Diagnosesoftware

Die Diagnosesoftware kann in zwei Gruppen untergliedert werden. Der maschinenresidente Teil der Diagnosesoftware befindet sich im ROM und führt nach Einschalten des Computers einen Eigentest durch. Mit dem Eigentest kann das System aber nicht vollständig getestet werden. Deshalb ist als zweiter Komplex ein Diagnosepaket vorhanden, das dem Anwender und dem Service-Techniker erlaubt, bei vermuteten Hardwarefehlern eine Diagnose des Systems vorzunehmen. Über ein Rahmenprogramm werden die verschiedenen Testprogramme von der Diskette aufgerufen und sowohl Existenztests auf Vorhandensein der zu testenden Baugruppen als auch Diagnosetests durchgeführt. Nähere Angaben zu den erwähnten Testprogrammen sind unter dem Hauptpunkt "Diagnose" zu finden.

# 5.2.3. Standardsoftware

Als Standardsoftware steht dem Anwender eine grosse Anzahl von Programmpäketen zur Verfügung. So unter anderem

- Datenbanksystem REDABAS-3

- Tabellenkalkulation MULTICALC

- Textprozessor TP

Geschäftsgrafik BGR

Informationsrecherchesystem AIDOS

- Tourenoptimierung TOUR

- Bearbeiten von SCP-Disketten unter DCP

- CAD-Systeme

Füer das Erarbeiten von Programmen in Maschinensprache können Entwicklungswerkzeuge eingesetzt werden, dié u.a. bestehen aus dem - Zeileneditor EDLIN

- bildschirmorientierten Editor BE

- Makroassembler MASM

- Linker LINK

- symbolischen Debugger SYMDEB

# 5.2.4. Programmiersprachen

Zur Erzeugung von Maschinenprogrammen können folgende problemorientierte Sprachen verwendet werden:

- BASIC-Interpreter

- BASIC-Compiler

- Standard-BASIC

- T-PASCAL

- FORTRAN

- C-Sprache

- Modula-2

# 7. Mess-, Steuerungs- und Regelungseinrichtungen

Mess-, Steuerungs- und Regelungseinrichtungen des EC 1834 sind in der Funktionsbeschreibung für die jeweilige elektronische Baugruppe aufgeführt.

# 8. Werkzeuge und Zubehör

(siehe "Verzeichnis der Ersatzteile, Werkzeuge und Zubehörteile")

9. Aufstellung und Montage

(siehe Software Dokumentation "Anleitung für den Bediener")

10. Kennzeichnung und Plombierung

Die Kennzeichnung ist entsprechend ST RGW 1361-78 und ST RGW 3185-81 am Gerät sowie ST RGW 258-80 an der Verpackung vorhanden.

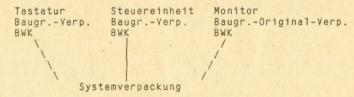

#### 11. Masse und Art der Verpackung

Für die einzelnen Baugruppen wurde eine Transportverpackung entwickelt, die den Belastungen im TUL-Prozess mittels Kleintransporter und bei Selbstabholung gerecht wird. Dabei wird davon ausgegangen, dass die dazugehörige Transportverpackung wiederverwendet wird. Zur Realisierung der Traktionsarten Eisenbahn, LKW und Schiff nach TGL 26465 wird für die verschiedenartigen Systemvarianten eine Reihe von Systemverpackungen auf der Basis von Sperrholzrahmenkisten eingeführt. Entsprechend der gesetzlichen Vorschriften sind diese einschliesslich der Innenverpackung in der DDR zumäckführungspflichtig.

Mindestfestigkeiten sind durch die Baugruppen bzw.das Gerät entsprechend TGL 26465 bzw. KROS 282/03 garantiert.Für den Drucker wird ebenfalls Originalverpackung benutzt.

#### III. Wartungsvorschrift

Die Wartungshinweise sind in den Technischen Beschreibungen der Baugruppen enthalten.

- VI. Verzeichnis der Ersatzteile, Werkzeuge und Zubehörteile

- 1. Ersatzteilliste

(Siehe "Ersatzteilkatalog")

- 2. Zubehörteile

- Netzkabel

- Systemdisketten (entsprechend Konfiguration)

- Staubschutzhaube

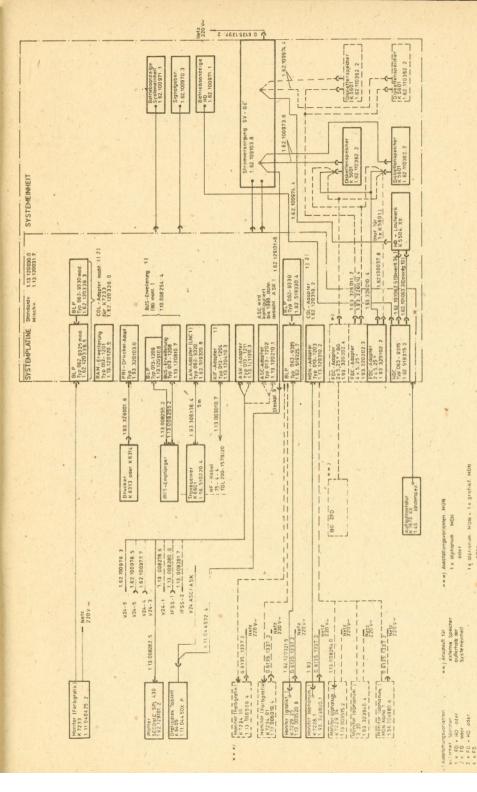

Personal-Computer EC 1834

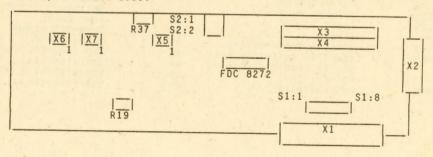

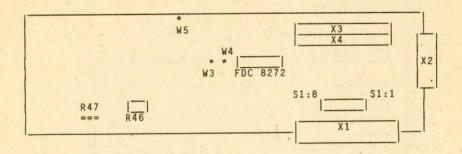

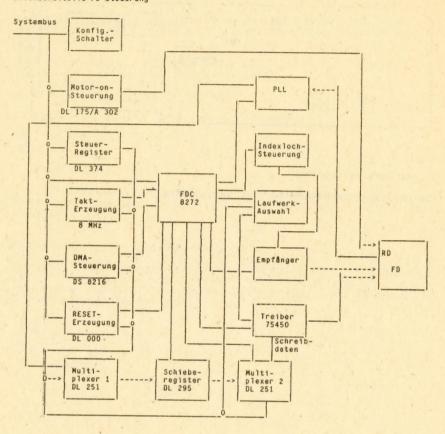

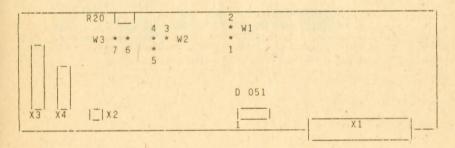

Gruppenverbindungsplan

1. 62.006002.4 117

1) Stackeinheit benotigt 2 Steckplätze

1x alphanum MON + 1x grafikt, MON

1x graffer, MON

21 nur alternativ steckbor

# Technische Beschreibung

\*\*\*\*\*\*\*\*\*\*\*\*\*

#### Inhaltsverzeichnis

- 1, Allgemeine Grundlagen

- 2. Signalbeschreibungen

- 3. Signalpegel

- 4. Mechanische Bedingungen

- Steckverbinderbelegungen

- 5.1. Steckverbinder 96-polig indirekt

- 5.2. Steckverbinder 62-polig direkt

1.62.540121.7 (GER) 085-3-000 852.53.01.004

Stand: 03/88

### 1. Allgemeine Grundlagen

Der BUS des PC EC 1834 wird durch Signalleitungen und Leitungen zur Stromversorgung der Adapter gebildet. Bezeichnet wird dieser als Systembus.

Er realisiert die Verbindung zwischen Systemplatine und den maximal acht Adaptern (Speichererweiterung, E/A-Adapter, BUS-Verlängerung) und steuert den Informationsaustausch zwischen diesen. Er ist geeignet zur Durchführung CPU- und DMA- gesteuerter Operationen.

### 2. Signalbeschreibungen

Die Signale des Systembusses gliedern sich in folgende Signalgruppen:

| Leitungsgruppe             | Anz.<br>Ltgen | Bezeichnung                   |

|----------------------------|---------------|-------------------------------|

| Datenbus                   | 16            | D15-D0                        |

| Adressbus                  | 20            | A19-A0                        |

| Steuerbus                  |               |                               |

| - DMA-u. REFRESH-Steuerung | 11            | DRQO-3, /DACKO-3, AEN, TC     |

| - Zugriffssteuerung        | 9             | /IOR, /IOW, /MEMR, /MEMW,     |

|                            |               | /MEMCS16, /BHE, ALE, /IOCHCK, |

|                            |               | IOCHRDY                       |

| - Interrupt                | 11            | IRQ9-12, IRQ14,15, IRQ3-7     |

| - Rücksetzen               | 1             | RESETDRY                      |

| Takt                       | 2             | CLK, OSC                      |

| Stromversorgung            | 8             | NOO, N5P, N5N, N12P, N12N     |

Beschreibung

Bedeutung der einzelnen Signale:

Signal E/A

|          | ezogen auf<br>stemplatine) |                                                                                                                                                                   |

|----------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| osc      | A                          | Oszillatortakt: Hochgeschwindigkeitstakt<br>mit einer Zykluszeit von 68 ns (14,7456<br>MHz)<br>Tastverhältnis 1:1                                                 |

| CLK      | A                          | Systemtakt: Er entsteht durch Division des<br>Oszillatortaktes durch drei und hat eine<br>Zykluszeit von 203 ns (4,9152 MHz); Tast-<br>verhältnis 1:2             |

| RESETDRY | A                          | Systemrücksetzen: HIGH- aktiv, Rücksetzen<br>der Systemlogik nach Netz-Einschalten oder<br>während eines Netzspannungsabfalls,<br>synchron zum Taktsignal         |

| A19-A0   | E/A                        | Adressbits 19-0: HIGH-aktiv, dienen der<br>Adressierung der systeminternen Speicher-<br>und E/A-Einheiten, werden vom Prozessor<br>oder der DMA-Einheit geliefert |

| D15-D0   | E/A                        | Datenbits 15-0: HIGH-aktiv, Datenbus für<br>Prozessor, Speicher und E/A-Einheiten                                                                                 |

| ALE                             | A   | Adressenverriegelung: HIGH-aktiv, dient der Übernahme gültiger Adressen in Adresslatch und der Verriegelung dieser mit H/L-Flanke, mit AEN verwendet dient es als Hinweis für gültige Prozessoradressen                                                                                                                                     |

|---------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /IOCHCK                         | - E | E/A-Kanal Fehler: LOW-aktiv, Anzeige eines<br>Paritätsfehlers in Speicher oder E/A-Ein-<br>heit bzw. Auswahl verbotener E/A-Adressen                                                                                                                                                                                                        |

| IOCHRDY                         | É   | E/A-Kanal bereit: HIGH-aktiv, im Normalfall HIGH; durch Speicher oder E/A-Einheiten auf LOW gesetzt wird die Verlängerung der BUS-Zyklen um weitere Taktzyklen (203 ns) erreicht; darf nicht länger als 10 Taktzyklen auf LOW gesetzt sein, um REFRESH-Vorgang nicht zu unterdrücken                                                        |

| IR09-12,<br>IR014,15,<br>IR03-7 | Ε   | Interruptanforderung 9-12, 14, 15, 3-7: HIGH-aktiv; signalisiert dem Prozessor, dass eine E/A-Einheit einen Eingriff for- dert, mit L/H-Flanke wird Interrupt ausge- löst, Signale bleiben bis zur Quittung durch Prozessor aktiv Prioritätsreihenfolge: IRQ9 - höchste IRQ10 IRQ11 IRQ12 IRQ14 IRQ15 IRQ3 IRQ4 IRQ5 IRQ6 IRQ7 - niedrigste |

| /10R                            | E/A | E/A-Lesebefehl: LOW-aktiv, ausgelöst durch<br>Prozessor bzw. DMA-Einheit, Anweisung an<br>E/A-Einheit, Daten auf Datenbus bereitzu-<br>stellen                                                                                                                                                                                              |

| /IOW                            | E/A | E/A-Schreibbefehl: LOW-aktiv, ausgelöst<br>durch Prozessor bzw. DMA-Einheit, Anweisung<br>an DMA-Einheit, Daten vom Datenbus zu über-<br>nehmen                                                                                                                                                                                             |

| /MEMR                           | Ę/A | Speicher-Lesebefehl: LOW-aktiv, ausgelöst<br>durch Prozessor bzw. DMA-Einheit, Anweisung<br>an Speicher, Daten auf Datenbus bereitzu-<br>stellen                                                                                                                                                                                            |

| /MEMW                           | E/A | Speicher-Schreibbefehl: LOW-aktiv, ausge-<br>löst durch Prozessor bzw. DMA-Einheit,<br>Anweisung an Speicher, Daten vom Datenbus<br>zu übernehmen                                                                                                                                                                                           |

| DRQ1-3   | E   | DMA-Anforderung: HIGH-aktiv, Anforderung von Peripherie-Geräten, um Zugriff zu DMA- Funktionen zu erlangen; Signal muss so lange aktiv sein, bis Anforderung mittels DACK-Leitung quittiert wird DRQ1 - höchste Priorität DRQ2 - niedrigste Priorität |

|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /DACK1-3 | A   | DMA-Antwort: LOW-aktiv, dienen zur Quittie-<br>rung der DMA-Anforderungen 1-3                                                                                                                                                                         |

| DRQ0     | Α   | DMA-Anforderung: HIGH-aktiv, REFRESH-Anfor-<br>derung vom Timer an DMA-Controller, aller<br>15 us aktiv                                                                                                                                               |

| /DACKO   | A   | DMA-Antwort: LOW-aktiv, REFRESH-Kennzei-<br>chen, dient für REFRESH des dynamischen<br>Speichers                                                                                                                                                      |

| AEN      | A   | Adress-Freigabe: HIGH-aktiv, Anzeige dass<br>DMA-Steuerung Kontrolle über Adress-, Da-<br>ten- und Steuerbus erlangt hat                                                                                                                              |

| TC       | A   | Ende-Zähler: HIGH-aktiv, wird Endezähler-<br>stand eines beliebigen DMA-Kanals erreicht,<br>liefert Signal HIGH-Impuls                                                                                                                                |

| /BHE     | E/A | BUS HIGH-Freigabe: LOW-aktiv, zeigt an,<br>dass auf höherwertigen Datenbits 15-8 gül-<br>tige Daten übertragen werden (bei 16-bit-<br>Operation)                                                                                                      |

| /MEMCS16 | E   | 16-bit-Speicherauswahl: LOW-aktiv, signalisiert der Systemplatine, dass die adressierte Speichereinrichtung mit 16-bit-Zugriffen betrieben werden kann                                                                                                |

| N 5P     |     | +5V±0,25V, Versorgungsspannung ungestützt                                                                                                                                                                                                             |

| N 5N     |     | -5 <u>V+</u> 0,25 <u>V</u> , Versorgungsspannung ungestätzt                                                                                                                                                                                           |

| N 12P    |     | +12V±0,6V, Versorgungsspannung ungestützt                                                                                                                                                                                                             |

| N 12N    |     | -12 <u>V+</u> 1,2V, Versorgungsspannung ungestützt                                                                                                                                                                                                    |

| N 00     |     | Zentrales Bezugspotential (Masse)                                                                                                                                                                                                                     |

|          |     |                                                                                                                                                                                                                                                       |

# 3. Signalpegel

Für alle logischen Bussignale müssen Sender bzw. Empfänger folgende Pegel bereitstellen bzw. verarbeiten:

|           | HIGH       | LOW        |

|-----------|------------|------------|

| Sender    | 2,4 5,25 V | 0 0,45 V   |

| Empfänger | 2,0 5,25 V | -0,5 0,8 V |

#### 4. Mechanische Bedingungen

Der Systembus ist auf der Systemplatine/MLL in Form gedruckter Leiterzüge realisiert. Er verbindet die acht Steckverbinder. welche zur Aufnahme der entsprechenden Adapter dienen. Die Steckverbinder sind in einem Abstand von 20,32 mm bestückt. Verwendet werden die Steckverbinder 96-polig nach EBS-GO 4007 (DIN 41612) Bauform R. Auf der Systemplatine befindet sich die Steckerleiste, auf den Adaptern die Buchsenleiste. Zur Nutzung von international im Angebot befindlichen Adapterplatten mit direkten Steckverbindern wird in Sonderfällen die System-

platine mit folgender Bestückung ausgeliefert:

zwei Steckplätze mit direkten Steckverbindern 62-polig nach DIN .... fünf Steckplätze mit indirekten Steckverbindern.

Die Adapter sind in beliebiger Reihenfolge in den Steckverbindern steckbar. Ausnahme bildet der Steckverbinderplatz 8 (nahe der SVE); er ist reserviert für spezielle Anwendungsfälle. Der Steckverbinderplatz 8 ist in Varianten mit BUS-Verlängerung für den BUS-Erweiterungsadapter vorgesehen, welcher mit einem Kabel von max. 1m Länge die Möglichkeit bietet, den Systembus zu verlängern. Die Grösse der Adapterleiterplatten sind 100 360/300/240/172,5 mm.

Die max. Bauhöhe auf den Adaptern beträgt 13,5 mm.

Auf jedem Adapter ist gewährleistet, dass alle Betriebsspannungen (auch nicht genutzte) gegen Masse mit Entstörkondensatoren 47 uF

und 0.1 uF abgeblockt sind.

Die Strombelastbarkeit pro Adapter bei N 5P lässt max. 3,4 A In der Summe aller acht Adapter können bei N 5P = 14 A. bei N 12P = 2 A, bei N 5N = 0.3 A und bei N 12N = 0.25 A verbraucht werden.

# 5. Steckverbinderbelegungen

# 5.1. Steckverbinder 96-polig indirekt

|                                                           | Rückwand der<br>A                        | Systemeinheit<br>B                                        | ć                                                                 |

|-----------------------------------------------------------|------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------|

| N 00<br>RESETDRV<br>N 5P<br>IRQ9<br>N 5N<br>DRQ2<br>N 12N | * 1<br>*<br>*<br>* 5<br>*                | * D8<br>* D9<br>* D10<br>* D11<br>* D12<br>* D13<br>* D14 | * /IOCHCK<br>* D7<br>* D6<br>* D5<br>* D4<br>* D3<br>* D2<br>* D1 |

| N 12P<br>N 00<br>/MEMW<br>/MEMR<br>/IOW<br>/IOR<br>/DACK3 | * 10 * * * * * * * * * * * * * * * * * * | * D15<br>*<br>*<br>*<br>*<br>*<br>*<br>*                  | * DO .<br>* IOCHRDY * AEN * A19 * A18 * A17 * A16                 |

| DRQ3<br>/DACK1<br>DRQ1<br>/DACKO<br>CLK<br>IRQ7<br>IRQ6   | * * * * * 20 *                           | * * * DRQ0 * * IRQ10 * IRQ11                              | * A15<br>* A14<br>* A13<br>* A12<br>* A11<br>* A10<br>* A9        |

| IRQ5<br>IRQ4<br>IRQ3<br>/DACK2<br>TC<br>ALE<br>N 5P       | * * 25 * * *                             | * IRQ12<br>* IRQ15<br>* IRQ14<br>* /MASTER                | * A8<br>* A7<br>* A6<br>* A5<br>* A4<br>* A3<br>* A2              |

| 0SC<br>N 00<br>N 00                                       | * 30<br>*<br>* 32                        | * N 5P<br>*<br>* /MEMCS16                                 | * A1<br>* A0<br>* /BHE                                            |

# 5.2. Steckverbinder 62-polig direkt

| Rückwand | der | Systemeinheit |

|----------|-----|---------------|

| R        |     | Λ             |

|          |     |   |   | MARKET STATE |

|----------|-----|---|---|--------------|

| N 00     | *   | 1 | * | /IOCHCK      |

| RESETDRY | k   |   | * | D7           |

| N 5P     | k   |   | * | D6           |

| IRQ9     | k   |   | * | D5           |

| N 5N     | k   | 5 | * | D4           |

| DRQ2     | k   |   | * | D3           |

| N 12N    | k   |   | * | D2           |

|          | k   |   | * | D1           |

| N 12P    | k   |   | * | DO           |

| N 00     | * 1 | 0 | * | IOCHRDY      |

| / HEHM   | k / |   | * | AEN          |

| \u2011   | k   |   | * | A19          |

| 11011    | *   |   | * | A18          |

| 1101     | t   |   | * | A17          |

| /DACK3   | 1   | 5 | * | A16          |

| DRQ3     |     |   | * | A15          |

| /DACK1   |     |   | * | A14          |

| DRQ1     |     |   | * | A13          |

| /DACKO * |     |   | * | A12          |

| CLK      | -   | 0 | * | A11          |

| IRQ7     |     |   | * | A10          |

| IRQ6     |     |   | * | A9           |

| IRQ5     |     |   | * | A8           |

| IRQ4     |     |   | * | A7           |

| IRQ3     | _   | 5 | * | A6           |

| /DACK2   |     |   | * | A5           |

| TC *     |     |   | * | A4           |

| ALE *    |     |   | * | A3           |

| N 5P *   |     |   | * | A2           |

| OSC *    |     | 0 | * | A1           |

| N 00 *   |     |   | * | AO           |

|          |     |   |   |              |

### Technische Beschreibung

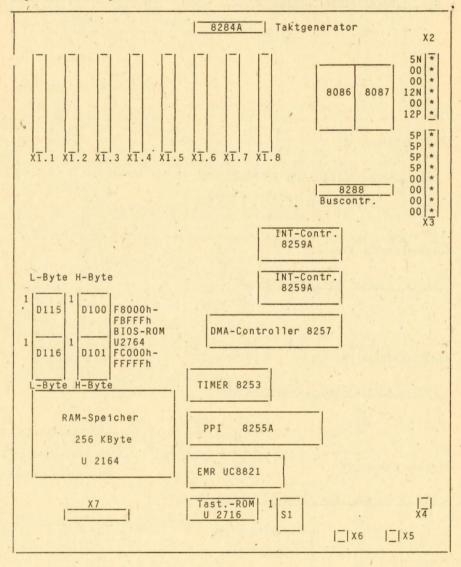

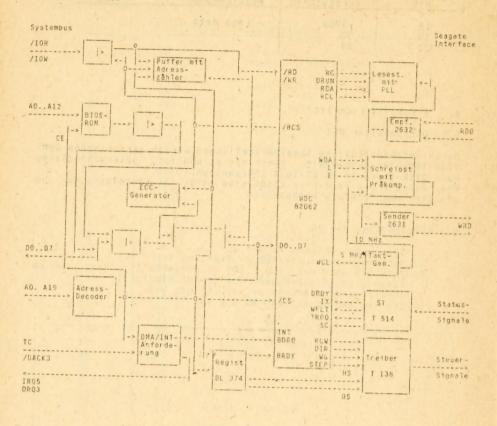

S y s t e m p l a t i n e (Typ 013-1200)

Personalcomputer robotron EC 1834

### Inhaltsverzeichnis

```

Verwendung und Einordnung

2.

Technische Daten

3.

Konstruktiver Aufbau

4.

Funktionsbeschreibung

Allgemeine Obersicht

4.1.

4.2.

Adressen-Zuordnung

4.2.1.

Speicher-Einteilung

4.2.2.

E/A-Adressenbereiche (Gesamtsystem)

E/A-Adressenbereiche (Systemplatine)

4.2.3.

4.3.

Takterzeugung

Mikroprozessor/Co-Prozessor

4.4.

4.5.

Systemzeitgeber

4.6.

Paralleles Peripheres Interface

4.7.

System-Unterbrechungen

4.8.

ROM-Speicher

4.9.

RAM-Speicher

E/A-Adressierung

4.10.

4.11.

DMA-Einrichtung

4.12.

Byte-Swap-Logik

4.12.1.

Anwendungszweck

4.12.2.

Wortzugriff auf Speicher mit 8 Bit-Datenbus

4.12.2.1. Speicher Schreiben

4.12.2.2. Speicher Lesen

E/A-Zugriff auf Tor mit ungerader Adresse

4.12.3.

DMA-Zugriff auf ungerade Speicheradresse

4.12.4.

4.13

NMI-Register

4.14.

Tastatur-Anschluss

Kontaktbelegung der Steckverbinder mit Kurzzeichenübersicht

5.

6.

Einstellvorschrift

7.

Wartungsvorschrift

```

1.62.540131.3 (GER) 085-3-000 851.53.01.001

Stand: 03/88

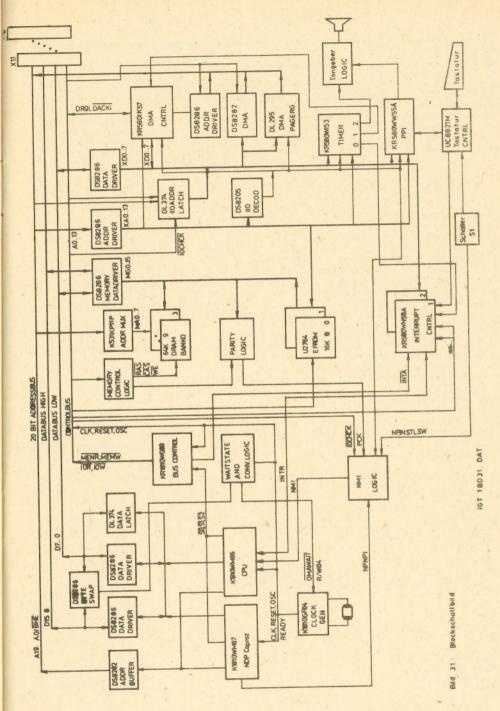

### 1. Verwendung und Einordnung

Die Systemplatine ist die zentrale Baugruppe des Personalcomputers EC1834. Sie enthält alle zur Steuerung des Gerätes notwendigen Funk-

tionsgruppen.

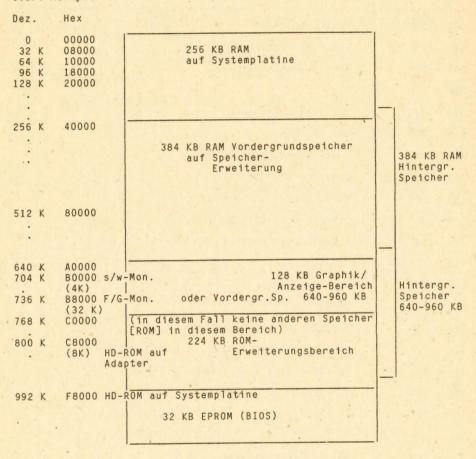

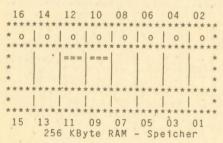

Die Steuerung des Gesamtsystems übernimmt der Mikroprozessor mit Hilfe einer Anzahl von hochintegrierten Peripherie-Schaltkreisen. Als Arbeitsspeicher sind auf der Systemplatine 256 KByte RAM integriert. Die CPU hat die Möglichkeit, 1 MByte Speicher zu adressieren, jedoch ist nur der Einsatz von max. 640 KByte als Vordergrundspeicher sinnvoll, bedingt durch die Speicherverwaltung von DCP.

Verwendung findet der Mikroprozessor KR 1810 WM 86 (analog i8086) mit 16-Bit-Datenbus und 20-Bit-Adressbus im Zeitmultiplexbetrieb, der Wortzugriff auf den Speicher ermöglicht. Die Arbeit mit der Peripherie

erfolgt im Byte-Zugriff.

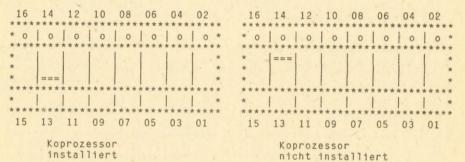

Der Co-Prozessor KR 1810 WM 87 (analog 18087) entlastet die CPU von

arithmetischen Operationen (Option).

Acht Steckplätze bieten die Möglichkeit, Peripheriebaugruppen über Adapter anzuschliessen bzw. den Speicher mit 384 KByte-Steckkarten als Vordergrund- oder als Hintergrundspeicher zu erweitern.

Auf der Systemplatine befinden sich weiterhin Steckverbinder für den

Anschluss der Tastatur sowie für den Tongeber.

#### 2. Technische Daten

Leiterplatte 240 mm x 360 mm MLL

Steckverbinder X4, X5, X6 Steckerleiste 2-pol.

202/1 TGL 55055

X7 Buchsenleiste 9-pol. 201-9 EBS-GO 4006/01-2-V GK2 LP abgewinkelt

X1.1...X1.8 Steckerleiste 96-pol.

332 EBS-G0 4007

Betriebsspannungen  $5P (+5V \pm 5\%)$ 12P (+12V  $\pm 5\%$ )

Mikroprozessor, Coprozessor als Option

Datenbus 16 Bit

Adressbus 20 Bit

Taktfrequenz 4,9152 MHz

Speicheradressraum 1 MByte

E/A-Adressraum/ 64 KByte.

15 priorisierte Interrupt-Niveaus

Operativspeicher 256 KByte dRAM mit Paritätskontrolle

erweiterbar auf 640 KByte

Festwertspeicher 32 KByte

#### Bauelementebasis

|                                                |                     | analog |

|------------------------------------------------|---------------------|--------|

| Mikroprozessor                                 | KR 1810 WM 86-5 MHz | 18086  |

| Arithmetischer Coprozessor                     | KR 1810 WM 87       | 18087  |

| Progr. Interrupt-Controller                    | KR 580 WN 59A       | 18259A |

| Taktgenerator                                  | KR 1810 GF 84       | 18284A |

| Bus-Controller                                 | KR 580 WG 88        | 18288  |

| Programmierbares Peripheres<br>Interface (PPI) | KR 580 WW 55A       | 18255A |

| Programmierbarer Intervall-<br>Timer           | KR 580 WI 53        | 18253  |

| DMA-Controller                                 | KR 580 IK 57        | 18257  |

| 64 K x 1bit dRAM                               | U 2164 C20          |        |

| 8 K x 8 EPROM                                  | U 2764 CC25         | 1 - 1  |

| - EMR für Tastaturinterface                    | UC 8821 M           |        |

| - 2 K x 8 EPROM für EMR                        | U 2716 C39          |        |

Erganzungsschaltkreise der Serien STTL und LSTTL

#### 3. Konstruktiver Aufbau

Die Systemplatine ist eine Mehrlagenleiterplatte mit 4 Informationsebenen, Masse- und Stromversorgungsebene der Grösse 240 mm x 360 mm und ist waagerecht in der Systemeinheit montiert. Sie besitzt drei Steckverbinder für den Tastaturanschluss (X7), den Tongeber (X4), die Betriebsspannungsanzeige und acht Steckverbinder X1.1 bis X1.8 für den Anschluss von 8 externen E/A-Einrichtungen mit Speichern über spezielle Adapter (z. B. Monitor für alphanumerische Darstellung, Farb-/Grafikadapter, Floppy Disk, Hard Disk, serielle Schnittstellen).

Die Gerätekonfiguration (Speicherausstattung, Typ des Monitors,

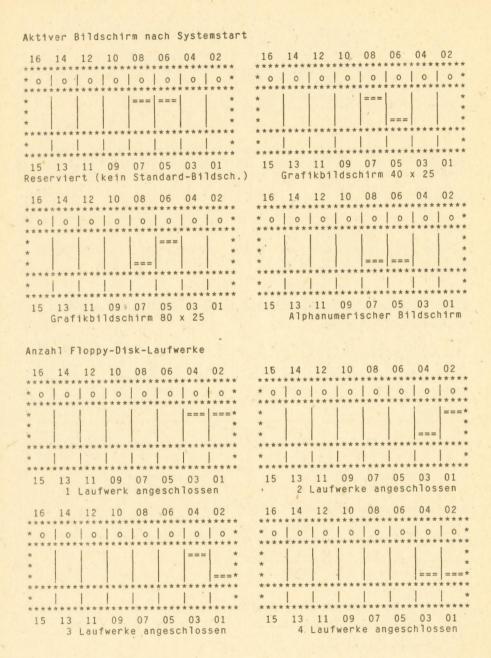

Die Gerätekonfiguration (Speicherausstattung, Typ des Monitors, Anzahl der Floppy Disk ist am DIL-Schalter S1 einstellbar.

#### 4. Funktionsbeschreibung

#### 4.1. Allgemeine Übersicht

Die Steuerung erfolgt mit einem Mikroprozessor des Typs K 1810 WM 86 (analog i8086), der eine Datenwegbreite von 16 Bit besitzt und einen Speicheradressbereich von 1 MByte ermöglicht. Der Prozessor wird im Maximum-Modus betrieben, so dass als Zusatzeinrichtung ein Coprozessor des Typs K 1810 WM 87 (analog i8087) eingesetzt werden kann (Steckfassung ist vorhanden). Der Prozessor arbeitet mit 4,915 MHz; diese Frequenz wird von einem Quarz der Frequenz 14,7456 MHz mittels Teilung

durch 3 gewonnen. Aus der Quarzfrequenz lassen sich die üblichen Baudraten der Übertragungseinrichtungen durch einfache Teilung ableiten. Bus-Zyklen bei Speicheroperationen dauern vier Taktzyklen von 203,5 ns, d.h. 814 ns. Dem gegenüber dauern E/A-Buszyklen generell fünf Taktzyklen, d. h. 1,017 us.

Der Prozessor wird durch einige LSI-Ergänzungsschaltkreise unterstützt, die vier 20-Bit DMA-Kanäle, drei 16-Bit Zeitgeber-Kanäle und 15 priorisierte Interrupt-Niveaus realisieren.

Drei der vier DMA-Kanäle stehen auf dem Systembus zur Verfügung und können für schnelle Datenübertragungen zwischen E/A-Einrichtungen und dem Speicher ohne Prozessoreingriffe verwendet werden. Der vierte DMA-Kanal wird für das Refreshen der dynamischen Speicher sowohl auf der Systemplatine als auch auf Speichererweiterungs-Adaptern verwendet. Dazu wird ein Zeigeberkanal so programmiert, dass er periodisch einen DMA-Zyklus anfordert. Mit dem dadurch ausgelösten Speicher-Lesezyklus wird ein Refreshen aller dynamischen RAM-Schaltkreise bewirkt.

Alle DMA-Übertragungen dauern 8 Prozessor-Taktzyklen bzw. 1,62 us (falls die Ready-Leitung nicht deaktiviert wird).

Die drei Zeitgeberkanäle werden folgendermassen benutzt: Kanal 1 für die periodische Anforderung von Refresh-Zyklen, Kanal 2 für die Tonerzeugung mittels des Tongebers und Kanal 0 als Konstant-Zeitbasis für den Systemzeitgeber.

den Systemzeitgeber. Yon den 15 priorisierten Interrupt-Niveaus stehen 11 auf dem Systembus für die Verwendung durch Adapterkarten zur Verfügung. Drei Interrupt-Niveaus werden auf der Systemplatine verwendet. Das Niveau O mit der höchsten Priorität ist mit dem Zeitgeberkanal 1 verbunden und erzeugt eine periodische Unterbrechung. Das Niveau 1 ist mit der Tastatursteuerung verbunden und erzeugt bei Empfang jedes Scan-Codes von der Tastatur eine Unterbrechung. Die nichtmaskierbare Unterbrechung (NMI) des Prozessors wird für die Behandlung von Paritätsfehlern, die Zusammenarbeit mit dem Co-Prozessor sowie für die virtuelle I/O-Adressierung genutzt. Die Systemplatine enthält RAM-und ROM- bzw. EPROM-Komplexe. Die RAM-Ausstattung beträgt 256 KByte mit Paritätskontrolle, die ROM-Ausstattung 32 KByte ohne Paritätsprüfung. Der ROM-Bereich enthält den Anfangstest nach Rücksetzen, einen Disketten-Bootstrap-Lader sowie das ROM-BIOS. Die Startadresse der CPU nach Rücksetzen liegt ebenfalls im ROM. Der Programm-Anlauf beginnt ab der Adresse FFFFOh.

### 4.2. Adressen-Zuordnung

# 4.2.1. Speicher-Einteilung

#### Start-Adresse

# 4.2.2. E/A-Adressenbereiche (Gesamtsystem)

| Hex. Adresse | Einrichtung                             |

|--------------|-----------------------------------------|

| 000 - 01F    | DMA-Controller                          |

| 020 - 03F    | Interrupt-Controller (1)                |

| 040 - 05F    | Timer-Schaltkreis                       |

| 060 - 07F    | PPI ) systemplatinen-                   |

| 080 - 09F    | DMA-Seitenregister ) intern             |

| OAO - OBF    | NMI-Register )                          |

| OCO - ODF    | Interrupt-Controller (2)                |

| OEO - OFF    | reserviert )                            |

| 1B0 - 1BF    | KIF-Adapter                             |

| 1E8 - 1EF    | Bank-Wechsel (RAM-Erweiterung)          |

| 210 - 21F    | Erweiterungs-Einheit (Bus-Verlängerung) |

| 278 - 27F    | /Parallel-Port 2 (Drucker)              |

| 2B0 - 2BF    | Monitor-Adapter                         |

| 2E0 - 2EB    | Serielles Port 2                        |

| 2F8 - 2FF    | Verbotener Adressenbereich (SP2)        |

| 320 - 32F    | Festplatten-Adapter                     |

| 378 - 37F    | Parallel-Port 1 (Drucker)               |

| 380 - 38F    | Verbotener Adressenbereich (SP1)        |

| 3A0 - 3AF    | " (SP1)                                 |

| 3B0 - 3BF    | " (MON)                                 |

| 3D0 - 3DF    | Farb-/Graphik-Adapter                   |

| 3E0 - 3EB    | Serielles Port 1                        |

| 3F0 - 3F7    | Disketten-Adapter                       |

| 3F8 - 3FF    | Verbotener Adressenbereich (SP1)        |

Wird durch einen E/A-Schreib- oder Lesebefehl eine Adresse der verbotenen Adressenbereiche angesprochen, so wird mittels IOCHCK = 0 ein NMI- ausgelöst, falls der jeweils zugeordnete Adapter vorhanden ist (SP1, SP2 - Serielles Port 1 bzw. 2; MON - Monitoradapter). Die angesprochene E/A-Adresse kann anschliessend über 080 und 081 gelesen werden.

# 4.2.3. E/A-Adressenbereiche (Systemplatine)

| Hex. R W Datenbus D7D0                                        |                                                              |

|---------------------------------------------------------------|--------------------------------------------------------------|

|                                                               |                                                              |

| 00 x x CH-0 DMA Address: A7 bi                                | s A0 if F/L = 0                                              |

| A15 bi                                                        | s A8 if $F/L = 1$                                            |

| 01 x x Terminal Count : C7 bi                                 | s CO if $F/L = 0$<br>C13 bis C8 if $F/L = 1$                 |

| 02                                                            | 013 013 00 11 172 1                                          |

| analog für CH-1 bis CH-3                                      | DMA                                                          |

| 07                                                            |                                                              |

| 08 X MODE SET : AL TC STATUS 0 0                              | S EW RP EN3 EN2 EN1 EN0<br>O UP TC3 TC2 TC1 TC0              |

| 08 X 31A103 0 0                                               |                                                              |

| 20 x Write ICW 1 (X'13' - E                                   | DGE, CASCADE, ICW4) Ini-                                     |

| 21 x Write ICW 2 (X'08' - I                                   | NT.ADDR 8) tiali-<br>RQ2 SLAVE) sierung<br>UFFRD, 8086 MODE) |

| 21 x Write ICW 3 (X'04' - I<br>21 x Write ICW 4 (X'09' - B    | UFFRD. 8086 MODE)                                            |

| 21 x Write OCW 1                                              |                                                              |

| 20 x Write OCW 2<br>20 x Write OCW 3                          | PIC1                                                         |

| 20                                                            |                                                              |

| 40 x Load Counter 0                                           |                                                              |

| 41 x " " 1.                                                   |                                                              |

| 42 x " " 2<br>x Write Mode Word (SC1,SC                       | O RI 1 RI O M2 M1 MO BCD)                                    |

|                                                               | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                      |

| 40 x Read Counter 0<br>41 x " 1                               | PIT                                                          |

| 42 x " " 2                                                    |                                                              |

| 43 x No Operation                                             |                                                              |

|                                                               |                                                              |

| 60 x Tastencode oder S1.                                      | PPI                                                          |

| 62 x Statusbits                                               |                                                              |

| 63 x Write CMD/MODE-Register                                  |                                                              |

| 81 x Write DMA Page Register                                  | CH-2 (0,0,0,0,A19,A18,A17,                                   |

| 82 x " " " "                                                  | A16)<br>CH-3                                                 |

| 83 x " " " "                                                  | CH-1                                                         |

| 80 x Read NMI Address: A7 bis<br>81 x Read NMI Address: 0, 0, | O, IOW, IOR, BHE, A9, A8                                     |

| 01 / 1000 1111 1100 1111                                      |                                                              |

| AO x Set NMI Mask (X'80')                                     |                                                              |

| AO X Clear NMI Mask (X'00')                                   |                                                              |

|                                                               |                                                              |

| CO x Write ICW1, OCW2 bzw. O                                  | SLAVE ID) ) siehe 20, 22                                     |

| Ca Linato Illia Illia IV III                                  | SLAVE IU) / STERE ZU, ZZ                                     |

| C1   X   Write ICW2, ICW3 (X'02' ICW4 bzw. OCW1               | PIC2                                                         |

#### 4.3. Takterzeugung

Zur Takterzeugung wird der Taktgenerator 8284A [D43] eingesetzt. Die-, ser Schaltkreis erfüllt drei Funktionen:

- Erzeugung des Systemtaktes und zweier weiterer Takte

- taktbezogene Bildung von RESET nach Einschalten

- taktbezogene Bildung von READY für die CPU

Der Taktgenerator bildet folgende Takte:

- CLK = 4.9152 MHz = 203 ns als Systemtakt

- PCLK = 2.45 MHz = 406 ns (intern)

- OSC = 14,7456 MHz= 68 ns (Quarzfrequenz)

CLK und OSC sind auf den BUS geführt, PCLK wird nur intern genutzt. Am RDY- und AEN-Eingang des Taktgenerators kann die CPU von der Peripherie in den WAIT-Zustand gesteuert werden. Dies wird während des DMA-Betriebes genutzt, und auch langsame Speicher und E/A-Einrichtungen schalten die CPU in den WAIT-Zustand.

### 4.4. Mikroprozessor/Co-Prozessor

Als Mikroprozessor findet die CPU 8086 [D20] Verwendung. Sie besitzt einen gemeinsamen Adress- und Datenbus mit 16 Daten- und 20 Adressleitungen, die über Latch-Register bzw. Treiber geführt werden [D2, D25, D26 für Adressbus; D 21, D23 für Datenbus]. Die CPU arbeitet im Maximum-Mode (MN/MX=LOW) und kann mit dem Arithmetik-Prozessor 8087 zusammenarbeiten. Beide Prozessoren sind dann über die Signale /TEST-/BUSY miteinander verbunden. Die Steuerung der Bus-Signale übernimmt der Bus-Controller 8288 [D4]. Er decodiert die Statussignale des Prozessors und leitet daraus die Steuersignale für die Adress-Latch-Register sowie die Datenbus-Treiber ab. Weiterhin übernimmt er die Steuerung der Interrupt-Bestätigung und bildet die Signale Speicher lesen (/MEMR), Speicher schreiben (/MEMW), E/A-Tor lesen (/IOR) und E/A-Tor schreiben (/IOW).

#### 4.5. System-Zeitgeber

Die Systemplatine des EC1834 enthält drei programmierbare Zeitgeber, die mit einem Timer-Schaltkreis 8253 [D53] realisiert sind. Für die Systemprogramme ist dieser Timer-Schaltkreis eine Einrichtung mit 4 E/A-Ports; drei E/A-Ports sind die Zeitgeberwerte und der vierte (Ausgabe-) Port ist das Register zur Modus-Steuerung. Die drei Zeitgeberkanäle werden im PC EC1834 folgendermassen verwendet:

Kanal 0 - Allgemeiner System-Zeitgeber

GATE 0 : 1

CLK IN 0 : 1,23 MHz

CLK OUT 0 : IRQO für Interrupt-Controller

Kanal 1 - Generator für Refresh-Anforderungen GATE 1 : 1 CLK IN 1 : 1,23 MHz CLK OUT 1 : 15 us Signal als Anforderung

Kanal 2 - Tongenerator für Tongeber

GATE 2 : Bit 0 von Port X'61' PPI

CLK IN 2 : 1,23 MHz

CLK OUT 2 : Ansteuerung Tongeber

Der TIMER-Schaltkreis wird mit der halben Frequenz von PCLK. also 1.23

MHz, getaktet.

Kanal O als allgemeiner System-Zeitgeber löst nach jeweils 100 ms einen Interrupt überIRQO zur Einstellung der Systemzeit aus. Kanal 1 dient zur Refresh-Anforderung für die dynamischen Speicher und bildet nach jeweils 15 us das Signal DRQO für den DMA-Schaltkreis, welches der Beginn eines Refresh-Zyklusses ist. Mit Kanal 2 wird der Tongeber angesteuert. Die Impulsfolge für den

Tongeber kann ausserdem noch vom PPI über den Eingang GATE2 des TIMER-

Schaltkreises beeinflusst werden.

#### 4.6. Paralleles Peripheres Interface

Der Schaltkreis 8255A [D54] ist ein paralleler Port mit drei Kanälen und dient der Abfrage bestimmter Zustände und der Ausgabe von Steuer-signalen auf der Systemplatine. Die Kanäle können einzeln wahlweise auf Ein- oder Ausgabe programmiert werden. Kanal A ist auf Eingabe programmiert und fragt den Konfigurationsschalter S1 ab, Kanal B ist auf Ausgabe und Kanal C auf Eingabe programmiert. An Kanal B und C sind Steuersignale aktiv. Die Belegung der PPI-Bits zeigt folgende Tabelle:

X'0060' PA O IPL von Diskette (Eingabe) 1 Coprozessor installiert 2 RAM ) Ausstattung 3 RAM ) Schal-4 ter S1 Display-Typ .1 5 6 ) Anzahl der 7 ) Diskettenlaufwerke Steuerung Zeitgeber-Kanal 2 (GATE 2) X'0061' PB 0 1 Steuerung Tongeber (Ausgabe) 2 P20 des EMR (UC 8821M) 3 - Enable RAM PCK 4 5 - Enable I/O CH CK P32 des EMR (UC 8821M) 6 7 P33 des EMR (" x'0062' PC 0 (Eingabe) 2 3 4 P34 des EMR (UC 8821M) 5 Zeitgeber 2 (CLK OUT 2) 6 I/OCHCK PCK

| - | PA2 PA3 | RAM-Ausstattung |

|---|---------|-----------------|

|   | 0 0     | 256 K           |

| PA4 | PA5 | Display-Typ                      |

|-----|-----|----------------------------------|

| 0 1 | 0 0 | reserviert                       |

| 0   | 1   | Farbmonitor 80x25<br>(s/w-Modus) |

| 1 1 | 1.  | s/w-Monitor                      |

| PAO PAI AIIZ | ahl Disketten-Laufwerke |

|--------------|-------------------------|

| 0 0 0        | 1 2                     |

| 1 0 1        | 3 4                     |

#### 4.7. System-Unterbrechungen

Mit dem NMI des Mikroprozessors und zwei Interrupt-Controller-Schaltkreisen 8259A [D48.D49] sind im PC EC1834 16 Unterbrechungsniveaus realisiert. Sie sind (in absteigender Priorität) folgendermassen zugeordnet:

NMI .

RAM-Paritätsfehler (Systemplatine bzw. RAM-Erweiterung), verbotene E/A-Adressen oder wahlweise Coprozessor

### Interrupt-Controller (8259A):

| IRQO        | System-Zeitgeber )             |        |                   |

|-------------|--------------------------------|--------|-------------------|

| IRQ1        | Tastatur )                     | syste  | emplatinen-intern |

| IRQ2        | Kaskadierung )                 |        |                   |

| IRQ8        | DMA-Endezähler Refresh)        |        |                   |

| IRQ9,10,11, |                                |        |                   |

| 12,14,15    |                                |        | verfügbar         |

| IRQ13       | reserviert/wahlweise Coprozess |        |                   |

| IRQ3        | serieller Adapter 2 bzw. KIF-A | dapter |                   |

| IRQ4        | serieller Adapter 1            |        |                   |

| IRQ5        | Festplatten-Adapter            |        |                   |

| IRQ6        | Disketten-Adapter              |        |                   |

| IRQ7        | Drucker-Adapter                |        |                   |

Es sind vier unterschiedliche Quellen vorhanden, die einen NMI auslösen können. Alle Quellen werden auf den NMI-Eingang der CPU geführt.

Beim Eintreten folgender Zustände wird ein NMI ausgelöst:

- Arithmetikprozessor (z.B. Division mit Null) - NPNPI

- Paritätsfehler des Systemplatinen-RAM -/PCK

- Paritätsfehler von Speichererweiterung oder Peripheriebaugruppen /IOCHCK

- virtuelle E/A-Adressierung /IOCHCK

Durch den Einsatz von zwei Interrupt-Controllern ist es möglich, mit 15 maskierbaren Interrupt-Ebenen zu arbeiten. Die Kaskadierung von zwei Interrupt-Controllern erfolgt so, dass der INT-Ausgang des Slave an einen IRQ-Eingang (Interrupt-Request) des Masters geführt ist (IRQ2 an D49). Das INT-Signal des Masters bewirkt bei der CPU die Interrupt-Anforderung INTR.

Die Anerkennung des Interrupts wiederum übernimmt der Bus-Controller und bestimmt den Zeitpunkt, zu dem der den Interrupt auslösende Controller-Schaltkreis seinen Interrupt-Vektor auf den Datenbus legt.

#### 4.8. ROM-Speicher

Der ROM-Speicher auf der Systemplatine besteht aus 2 (max.4) EPROM-Schaltkreisen 8 K x 8 Bit K 573 RF4 bzw. U 2764 C25 [D100,101,D115,116]. Er ist als 8 K x 16-Bit-Speicher realisiert; der Code für gerade bzw. ungerade Adressen befindet sich jeweils in unterschiedlichen Schaltkreisen.

Der Adressenbereich des ROM-Speichers befindet sich am Ende des gesamten 1 MByte CPU-Adressenbereichs ab Adresse F8000h. Es wird keine Paritätsprüfung ausgeführt, dafür erfolgt eine Prüfsummenbildung über

alle vier Schaltkreise.

Die Decodierung einer Speicheradresse für den ROM übernimmt ein 8-fach-NAND [D5], das bei aktiven Adressleitungen A15...A19 das Signal /ROMADRSEL bildet. Damit wird ein 1-aus-8-Decoder SEO5 [D66] freigegeben, der aus der Adressleitung A14 entweder die Speicherbank ab F8000h [D115,D100] (A14=LOW) oder ab FC000h [D116,D101] auswählt (A14=HIGH).

#### 4.9. RAM-Speicher

Der RAM-Speicher auf der Systemplatine besteht aus 36 RAM-Schaltkreisen 64K X 1 Bit U 2164 C20. Er ermöglicht 16-Bit-Zugriffe durch die CPU. Organisationsmässig ist er als 128K x 16 Bit aufgebaut. Eine Paritätslogik ergänzt jedes Byte auf gerade Parität in einem zusätzlichen Speicherschaltkreis, die beim Lesen wieder geprüft wird. Im Fehlerfall wird ein NMI durch /PCK (/IOCHCK bei Speichererweiterung) ausgelöst.

Der Adressbereich des RAM auf der Systemplatine ist 00000h...3FFFFh. Die Speichererweiterung liegt im Bereich von 4000h...9FFFFh (Vorder-

grundspeicher).

Die Decodierung einer RAM-Speicheradresse erfolgt mittels eines 1-aus-8-Decoders [D65], der in Abhängigkeit vom Pegel der Adressleitung A17 eine Speicherbank von 128 KByte auswählt.

A17 = 0 --> Adressbereich 0...128K --> /RAS1 A17 = 1 --> Adressbereich 128K...256K --> /RAS0

Ein 128-KByte-Bereich wiederum ist in zwei Bänke zu je 64 KByte unterteilt, in denen sich bei 16-Bit-Zugriff jeweils L-Teil und H-Teil einer Adresse befinden, bei Byte-Zugriff in einer 64-K-Bank Bytes mit gerader Adresse und in der anderen 64K-Bank Bytes mit ungerader Adresse. Diese Zuordnung ist abhängig von den Signalen AO und /BHE und kann folgender Tabelle entnommen werden:

| AO /BHE | CAS             |                                               |

|---------|-----------------|-----------------------------------------------|

| LLL     | /CASL=L,/CASH=L | Wortzugriff                                   |

| LH      | /CASL=L,/CASH=H | Bytezugriff auf gerade<br>Adresse (DOD7)      |

| H L     | /CASL=H,/CASH=L | Bytezugriff auf ungera-<br>de Adresse (D8D15) |

Die Adressleitungen Al...A16 liegen über Adressmultiplexer SY57 [D85,86] an den Speicherschaltkreisen an. Mit /RAS=L, decodiert aus /MEMR oder /MEMW und Adresse, und ADRSEL=L werden die Adressleitungen Al...A8 an eine Bank von 128 KByte geschaltet. Das Signal Speicherzugriff (/MEMR oder /MEMW) wird über D-FF D58 geleitet und bildet um

zwei OSC-Takte verzögert das Signal ADRSEL=H, mit dem der Adressmultiplexer umgeschaltet wird und die Adressen A9...A16 an die ausgewählte Speicherbank legt. Nach nochmaliger Verzögerung über ein weiteres D-FF [D67/5] wird das durch AO und /BHE ausgewählte CAS-Signal gebildet. Damit ist die vollständige Adresse an den ausgewählten Speicherbereich angelegt und kann durch die CPU oder den DMA gelesen oder beschrieben werden. Zwei bidirektionale 8-Bit-Treiber [D111,112] für DO...D7 bzw. D8...D15 schalten den Datenbus in Abhängigkeit von /MEMR und werden ausgewählt durch /MEMADRSEL und AO für gerade Adressen bei Bytezugriff bzw. L-Byte bei Wortzugriff und /BHE für ungerade Adressen bei Byte-Zugriff bzw. H-Byte bei Wortzugriff. Die Paritätslogik besteht aus dem 9. Speicherschaltkreis einer jeden 64K-Bank sowie einem Paritätsdetektor SY80 [D114] für ungerade Adressen und einem Paritätsdetektor [D113] für gerade Adressen sowie der Logik zum Auswerten von Paritätsfehlern, die auf gerade Patität prüft. Bei auftretenden Paritätsfehlern beim Lesen wird das Signal /PCK=L gebildet, welches den NMI auslöst.

REFRESH:

Ein Refresh-Zyklus wird nach jeweils 15 us durch den TIMER-Schaltkreis über den DMA angefordert und in der Speichersteuerung mit DACKO=H eingeleitet. Mit /DACKO=L und /MEMR=L vom DMA werden beide RAS-Signale aktiv geschaltet [D70/3,6]. Die Bildung von ADRSEL und CAS wird durch Sperren des ersten Verzögerungs-FF's [D58/5] verhindert. Der Adress-Multiplexer [D85,86] schaltet mit ADRSEL=L die Adressleitungen A1...A7 zum Speicher durch, A0 wird mit DACKO=H statt A8 an D68/6 durchgeschaltet und /RASO, /RAS1=L aktivieren sämtliche Speicherschaltkreise. Somit werden mit jedem Refresh-Zyklus 256 Bit eines jeden Speicherschaltkreises "gelesen" und damit regeneriert. Nach einem DMA-Durchlauf mit 256 Zyklen ist der gesamte dynamische RAM-Speicher aufgefrischt.

#### 4.10. E/A-Adressierung

Bei E/A-Schreib-/Lesezyklen erfolgt die Adressierung analog zur Speicheradressierung über die Adressbit A19-A0.

Da maximal nur 64 KByte E/A-Register adressiert werden können, liegt die jeweils gültige Adresse auf den Adressleitungen A15-A0. Die Adressleitungen A19-A16 sind standardmässig auf L-Pegel. Der PC EC 1834 lässt die Adressierung von maximal 1024 E/A-Adressen zu. Die ersten 258 E/A-Adressen werden für die Systemplatine reserviert, die restlichen 768 können auf Adaptern genutzt werden.

### 4.11. DMA-Einrichtung

Die Systemplatine enthält eine DMA-Einrichtung mit 4 DMA-Kanälen auf der Basis eines DMA-Controllers 8257. Der DMA-Kanal 0 (mit der höchsten Priorität) wird intern auf der Systemplatine verwendet, die drei DMA-Kanäle 1-3 stehen auf dem Systembus für die Verwendung durch Adapter zur Verfügung.

Es besteht folgende Zuordnung:

Kanal 0 - Refresh-Steuerung

Kanal 1 - KIF-Adapter

Kanal 2 - Floppy-Disk-Controller Kanal 3 - Hard-Disk-Controller Der DMA-Schaltkreis 8257 [D50] steuert den Datenaustausch zwischen Speicher und E/A-Geräten und umgekehrt. Von der Peripherie bzw. dem TIMER-Schaltkreis (bei Refresh) erhält der 8257 eine DMA-Anforderung, die er bei Erlangen der Busherrschaft von der CPU mit dem Signal DACK an die Peripherie bestätigt. Der DMA-Betrieb wird so lange aufrechterhalten, wie die DMA-Anforderung DRO aktiv bleibt oder eine DMA-Anforderung an einen höherpriorisierten Kanal gelangt. Nach jeder Byte-Obertragung wird die Speicheradresse um 1 erhöht.

Der DMA operiert mit 16-Bit-Adressen und kann daher nur innerhalb eines 64 KByte-Adressraumes DMA-Zyklen ausführen. Die Page (64 KByte-Seite) muss deshalb in einem gesonderten Register durch die CPU be-

reitgestellt werden,

Die maximale Länge eines DMA-Durchlaufes kann 16 KByte betragen. Den Zählwert enthält ein 14 Bit-Register des DMA, der bei Nulldurchlauf des Zählers das Signal TC (Terminal Count) an die Peripherie sendet

und damit die Beendigung eines DMA-Zyklusses signalisiert.

Die Page-Register [D6,D28,D29] sind 4 Bit-Schieberegister, die jeweils für einen externen DMA-Kanal die Adressen Al6...Al9 bereitstellen. Sie werden durch die CPU mittels OUT-Befehl 80...83 eingestellt. Nach der DMA-Anforderung (DROO...DRQ3) sendet der 8257 HRQDMA zur Erlangung der Busherrschaft. Eine Überwachungsschaltung [D3/8] beobachtet die Statusleitungen des Prozessors und setzt bei Eintritt der CPU in den Status "Unterbrechungsannahme" (/SO.../S2=H) ein D-FF [D38/9]. Mit dem nächsten Takt CLK86 wird ein weiteres D-FF gesetzt [D51/5], welches das Signal HOLDA als Bestätigung für die Erlangung der Busherrschaft an den DMA-Schaltkreis sendet. Der folgende Takt CLK veranlasst über ein 4-fach-D-FF u. a. die Bildung des Signales AENBRD=H, welches die Adress-und Datebustreiber der CPU inaktiv schaltet. Ein weiterer Takt an D35 führt zur Bildung von /DMAAEN, mit dem die Adresstreiber [D64,D45] des DMA-Schaltkreises aktiviert werden und von /DMAWAIT. Mit diesem Signal, ausgewertet am Taktgeberschaltkreis [D43], wird die CPU in den WAIT-Zustand bis zur Beendigung des DMA-Übertragungszyklusses gesteuert. Die Erlangung der Busherrschaft durch den DMA-Schaltkreis wird mit DACKO...3 an die Peripherie quittiert.

Im nächsten Schritt gibt der 8257 über seinen Datenbus (D0...D7) den

Im nächsten Schritt gibt der 8257 über seinen Datenbus (DO...D7) den H-Teil der Speicheradresse aus, von der gelesen bzw. in die geschrieben werden soll. Diese Adresse wird in einem Register SE82 [D45] zwischengespeichert. Anschliessend erfolgt an den Adressausgängen AO...A7 die Ausgabe des L-Teiles der Adresse, die über dem Treiber

SE86 [D64] auf dem Adressbus liegen.

Weiterhin wird Über einen Treiber SE16 [D61] das Signal /BHE nachgebi]det, aus dem in der Speichersteuerung die Bank mit ungeraden Adres-

sen ausgewählt wird.

Mit Anliegen der kompletten 20-Bit-Adresse werden nun vom DMA-Schaltkreis die Steuersignale für Speicher lesen bzw. Speicher schreiben (/MEMR,/MEMW) und Peripherie schreiben bzw. lesen (/IOW,/IOR) generiert.

DMA-read-Zyklus: Speicher lesen - MEMR aktiv E/A-Port schreiben-IOW aktiv DMA-write-Zyklus Speicher schreiben-MEMW aktiv E/A-Port lesen -IOR aktiv

Eine Ausnahme bildet der Refresh-Zyklus, bei dem nur das Signal MEMR

aktiv sein muss.

Nach erfolgreicher Übertragung wird das TC-Register des DMA um eins vermindert und die Adresse um eins erhöht. Die Bus-Herrschaft wird an die CPU zurückgegeben, falls DRQ wieder LOW ist. In Diesem Fall wird HRQ inaktiv geschaltet und somit der WAIT-Status des Prozessors aufgehoben. Wenn DRQ weiter aktiv (HIGH) bleibt, wird der nächste DMA-Zyklus ausgeführt, der nur durch eine höherpriorisierte DMA-Anforderung (z.B. REFRESH) unterbrochen werden kann.

#### 4.12. Byte-Swap-Logik

#### 4.12.1. Anwendungszweck

Der grundlegende Unterschied des Prozessors 8086 im EC 1834 zum 8088, der zumeist in den internationalen Typen vergleichbarer Personalcomputer. Anwendung findet, besteht im Einsatz eines 16 Bit-Datenbusses beim 8086.

Praktisch bedeutet das, dass Mikroprozessoren mit 8 Bit-Datenbus (8088) auf Speicherplätze nur byteweise zugreifen können, auch wenn sie intern 16 Bit Verarbeitungsbreite besitzen. Der Vorteil des Einsatzes des 8086 besteht also darin, dass die CPU entsprechend ihrer internen Verarbeitungsbreite von 16 Bit auch wortweise auf Speicher zugreifen kann, d.h. das L-Byte (mit gerader Adresse) liegt auf dem Datenbus DO...D7 (AO=LOW), das H-Byte (mit ungerader Adresse) auf dem Datenbus D8...D15 (/BHE=LOW). Dadurch können Programme bis zu 30 % schneller sein als PC's mit 8088-CPU.

Bei Speicherzugriffen auf den Arbeitsspeicher von max 640 KByte im EC 1834 hat die Byte-Swap-Logik keinen Einfluss, denn sie wird über /MEMCS16=LOW (Speichererweiterung) bzw./MEMADRSEL=LOW (Systemplatine, ROM- oder RAM-Zugriff) abgeschaltet, und der Speicherzugriff kann wortweise oder byteweise über DO...D15 erfolgen.

Notwendig wird die Byte-Swap-Einrichtung sowohl um der Forderung zu genügen, international im Angebot befindliche Erweiterungsadapter mit 8 Bit-Bus-Speichern einsetzen zu können als auch E/A-Befehle und DMA-

Zugriffe auf ungerade Adressen zu ermöglichen.

Die Aufgabe der Byte-Swap-Einrichtung besteht darin, den H-Teil des Datenbusses der CPU 8086 (D8...D15) bei Wortzugriff zeitgerecht auf den Datenbus DO...D7 von 8 Bit-Peripherie bzw. deren Speichereinrichtungen umzulenken und umgekehrt. Weiterhin muss der Datenbus bei 8 Bit-Zugriffen (E/A, DMA) auf unge-

rade Adressen umgeschaltet werden:

- D8...D15 auf DO...D7 bei OUT-Befehlen

- D0...D7 auf D8...D15 bei IN-Befehlen - D0...D7 auf D8...D15 beim DMA-Speicher-Schreib-Zyklus - D8...D15 auf DO...D7 beim DMA-Speicher-Lese-Zyklus

Unter drei verschiedenen Bedingungen ist die Benutzung der Byte-Swap-Logik also notwendig:

wortweiser Zugriff auf Speicher mit 8 Bit-Bus

E/A-Zugriff auf Tor mit ungerader Adresse

DMA-Zugriff auf ungerade Speicheradresse

# 4.12.2. Wortzugriff auf Speicher mit 8 Bit-Datenbus

#### 4.12.2.1. Speicher schreiben

Nach Ausgabe der Speicheradresse, dem 16 Bit-Datenbus DO...D15 und MEMW wird die CPU über /R-W84 in WAIT gesteuert [FF D38/5=LOW], wobei Daten und Adressen von der CPU weiter anliegen. /CS86H und /CS86L sind durch DEN (data enable) vom Bus-Controller, /BHE=LOW und AO=LOW (immer LOW bei Wortzugriff) aktiv geschalten und geben Datenbustreiber [D21, D23] der CPU frei. Somit wird das L-Byte (DO...D7) in die adressierte Speicherzelle eingetragen. Da die CPU weiter im WAIT-Zustand bleibt, wird mit Hilfe einer Flip-Flop-Kette [D15/5, D36] ein zweiter Speicher-Schreib-Zyklus, synchronisiert mit dem Systemtakt, nachgebildet, so dass auch das H-Byte (D8...D15) den Speicher übergeben werden kann.

/MEMW für den Speicher neu zu aktivieren (Flanke notwendig). Mit dem nächsten Takt wird ein D-FF [D15/9] gesetzt, welches /CS86L inaktiv schaltet, die Adressleitung AO von LOW auf HIGH setzt und CS für einen 8 Bit-Treiber [D22] bildet, der den Datenbus D8...D15 von der CPU auf den Datenbus D0...D7 für die Speicher schaltet. Die Datenflussrichtung des Treibers wird durch das Signal DT-/R=LOW (data transmit-/read) vom Bus-Controller bestimmt. Somit wird also im zweiten Speicher-Schreib-Zyklus der H-Teil des Datenbusses der CPU auf die Datenleitungen D0...D7 für den Speicherzugriff umgelenkt. Anschliessend wird der WAIT-Zustand der CPU wieder aufgehoben.

# 4.12.2.2. Speicher lesen

Der Ablauf des Speicherzugriffes beim wortweisen Lesen durch die CPU aus Speichern mit 8 Bit-Datenbus ist prinzipiell der gleiche. Zusätz-lich muss noch die Voraussetzung geschaffen werden, dass der CPU, wenn sie den WALT-Zustand verlässt, ein 16 Bit breites Datenwort zur Verfügung steht. Deshalb wird der Inhalt der ersten durch die CPU adressierten Speicherzelle (mit gerader Adresse in einem Latch-Register [D24] zwischengepuffert. Einen Systemtakt später schaltet AO von LOW nach HIGH, und der Datenbustreiber zur Umlenkung der Datenleitungen DO...D7 vom Speicher auf D8...D15 der CPU sowie das Latch-Register [D24] für DO...D7 werden freigegeben. Wieder einen Systemtakt später wird die CPU aus dem WAIT-Zustand entlassen und kann von ADO...AD7 und D8...D15 ein komplettes 16 Bit-Wort übernehmen.

# 4.12.3. E/A-Zugriff auf Tore mit ungerader Adresse

Die Daten für ungerade Ausgabe-Toradressen gibt die CPU auf D8...D15 aus und erwartet auch bei Eingabebefehlen von ungeraden Adressen die Daten auf D8...D15.

Es sind grundsätzlich nur byteweise E/A-Befehle zugelassen. Eine Überwachungslogik [D32/3] sorgt dafür, dass bei wortweisen E/A-Befehlen der 8 Bit-Treiber [D22] für die Umlenkung des Datenbusses nicht freigegeben wird.

Die Richtungsvorgabe für den Datenbustreiber erfolgt entsprechend des Signalpegels von DT-/R in Abhängigkeit von IOR bzw. IOW. CS für D22 schaltet am NAND D11/6.

# 4.12.4. DMA-Zugriff auf ungerade Speicheradresse

Bei DMA-Zugriff auf ungerade Speicheradresse wird mit /AEN=LOW der Bus-Controller inaktiv geschaltet, so dass die Signale /MEMR oder /MEMW vom DMA gültig sind. Mit AO=HIGH schaltet CS für den Treiber zur Umlenkung des Datenbusses [D22]. Die Datenflussrichtung des Treibers wird mit /XMEMW des DMA eingestellt.

#### 4.13. NMI-Register

Ein nichtmaskierbarer Interrupt (NMI) kann von vier unterschiedlichen Quellen ausgelöst werden (siehe 4.7.). Das Signal /IOCHCK wird aktiv bei Paritätsfehlern der Speichererweiterung und bei E/A-Befehlen auf verbotene Toradressen (siehe 4.2.2.). Vom System ist also nicht erkennbar, welche Quelle den NMI ausgelöst hat. Deshalb wird mit Auftreten von /IOCHCK der augenblickliche Zustand des Adressbusses AO...A9 sowie der Steuersignale /IOR, /IOW und /BHE in Latch-Registern [D30, D31] festgehalten und kann in der Interrupt-Behandlungsroutine über

die Toradressen 80 und 81 gelesen und ausgewertet werden. Damit ist die Unterscheidung von Speicher-Paritätsfehlern und E/A-Zugriffen auf verbotene Adressen gewährleistet. Co-Prozessor und Paritätsfehler Die beiden anderen NMI-Quellen,

Systemplatinen-RAM (PCK) werden folgendermassen unterschieden:

- Co-Prozessor meldet zusätzlich IRQ 13

- PCK kann über Port C Eingang 7 des PPI abgefragt werden

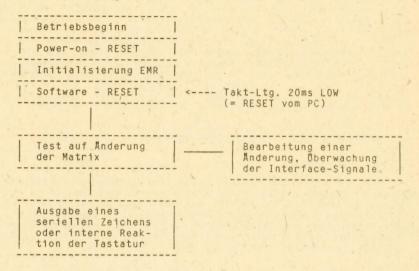

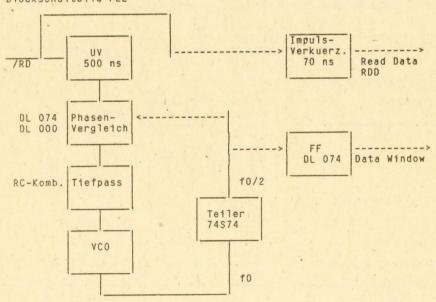

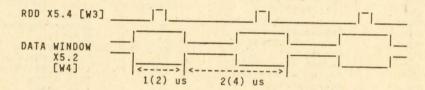

#### 4.14. Tastatur-Anschluss

Den Tastatur-Anschluss realisiert ein Einchip-Mikrorechner UC 8821 [D55]. der mit einem EMR UC 8820 auf der Tastatur korrespondiert. Das Programm für den EMR ist in einem 2 K-EPROM U 2716 [D56] enthalten. Daten werden nur von der Tastatur zum System mit KBCLK und KBDATA gesendet (XT-MODUS). Die übrigen angeschlossenen Ports dienen der Steuerung des EMR bzw. der Abfrage des Konfigurationsschalters S1, dessen Schalterinformation an den PPI übergeben wird. Portbelegung:

Obernahme Schalterstellung Konfigurationsschalter S1 Port 0: Port 1: bidirektionales Dateninterface zwischen PPI und EMR

Port 2: Steuerleitung vom PPI

P30/P31 - Testen der Signale auf den Leitungen KBDATA und Port 3: KBCLK

P32/P33 - Steuerleitung vom PPI P34 - Steuerleitung zum PPI P35 - Bildung von KBCLK P36 - Bildung von IRQ1 P37 - Bildung von KBDATA

Der EMR hat folgende Aufgaben zu erfüllen:

- Steuerung des Tastatur-Interface und Serien-/Parallel-Wandlung sowie Paritätsprüfung und -generierung, Zeitüberwachung

- Erzeugung des Interrupt-Signales IRQ1 nach Empfang eines gültigen SCAN-Codes

- Übertragung der Schalterinformation zum PPI - Selbsttest nach dem Einschalten

5. Kontaktbelegung der Steckverbinder mit Kurzzeichenübersicht Steckverbinder X1.1...X1.8: siehe Bus-Richtlinie PC EC 1834 Steckverbinder X2:

| PIN                   | Kurzzeichen                        | Bezeichnung |

|-----------------------|------------------------------------|-------------|

| 1<br>2<br>3<br>4<br>5 | 12P<br>00<br>12N<br>00<br>00<br>5N |             |

# Steckverbinder X3:

| PIN | Kurzzeichen | Bezeichnung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |