## Michael Roth

## **MIKROPROZESSOREN**

Wesen - Technologie - Weiterentwicklung

Aufbau - Programmierung - Anwendung

**KDT-Hochschulsektion**

Wissenschaftliche Zeitschrift

Technische Hochschule Ilmenau

## Michael Roth

# Mikroprozessoren

Wesen - Technologie - Weiterentwicklung Aufbau - Programmierung - Anwendung

#### Vorwort

Mikroprozessoren bieten als hochintegrierte Rechner-Zentraleinheiten die Möglichkeit zu einer neuen Qualität der Informationsverarbeitung in einer außerordentlichen Vielzahl von Geräten, Maschinen und Anlagen der Produktion und der Konsumtion.

Die Leistungsfähigkeit dieser Erzeugnisse, ihre Gebrauchswerte, Qualität, Zuverlässigkeit und moralische Lebensdauer werden in immer stärkerem Maße durch das Niveau ihrer Informationsverarbeitung bestimmt.

Die Mikroelektronik stellt mit ihrem leistungsfähigsten Erzeugnis, dem Mikroprozessor, der Volkswirtschaft ein wesentliches technisches Mittel bereit, hochanspruchsvolle Aufgaben zu erfüllen. Der Entwicklungsingenieur erhält damit ein faszinierendes Bauelement in die Hand. Es gestattet ihm, alte Lösungen wesentlich zu verbessern und vor allem neue Gebrauchswerte zu finden.

Für die Hilfe beim kurzfristigen Erarbeiten der vorliegenden Schrift möchte ich Prof. M. Kehle, Vorsitzender der KDT-Hochschulsektion, und Prof. W. Liebich, Leiter des Fachbereiches Informationsverarbeitung der Sektion TBK, meinen herzlichen Dank aussprechen.

Ilmenau 1977

Doz. Dr.-Ing. M. Roth

VED RFT Meßelektronik Gresden Entwicklungsstelle Leipzig 7827 Leipzig Untere Giehstädtetr. 12-14 Zur zweiten Auflage

Die Fortschritte der Mikroelektronik international und in der DDR gestatten immer mehr eine erfolgreiche Nutzung dieser Technik. Es ist das Anliegen der erweiterten zweiten Auflage, dem entsprechend gewachsenen Informationsbedürfnis sowohl zur DDR-Technik als auch zu internationalen Mikroprozessor-Systemen zu entsprechen.

Ilmenau, 1978

Doz. Dr.-Ing. M. Roth

#### Dritte Auflage

Die vorliegende dritte Auflage ist mit Ausnahme der Korrekturen gegenüber der zweiten Auflage unveründert.

Ilmenau, 1978

Prof. Dr.-Ing. M. Roth

#### Mikroprozessoren

### Wesen - Technologie - Weiterentwicklung -Aufbau - Programmierung - Anwendung

#### Inhaltsangaben

| 0.      | Einleitung                                                             | 7  |  |  |

|---------|------------------------------------------------------------------------|----|--|--|

| 1.      | Technologie und Entwicklungstendenzen elektroni-<br>scher Schaltkreise | 10 |  |  |

| 1.1.    | Schaltkreis-Fertigungsprozeß                                           | 10 |  |  |

| 1.1.1.  | Klassischer Herstellungsprozeß mikroelektroni-                         |    |  |  |

| 1.1.2.  | Weiterentwicklung der Fertigungeverfahren                              | 12 |  |  |

| 1.2.    | Schaltungstechnische Elemente mikroelektroni-                          | 14 |  |  |

|         | scher Schaltkreise                                                     |    |  |  |

| 1.2.1.  | TTL-Schaltkreise                                                       | 14 |  |  |

| 1,2,2,  | PMOS-Schaltkreise                                                      | 16 |  |  |

| 1,2.3.  | NMOS-Schaltkreise                                                      | 16 |  |  |

| 1.2.4.  | CMOS-Schaltkreise                                                      | 17 |  |  |

| 1.2.5.  | ECL-Schaltkreise                                                       | 18 |  |  |

| 1.2.6.  | FAMOS-Speicherzelle                                                    | 19 |  |  |

| 1.2.7.  | MNOS-Speicherzelle                                                     | 20 |  |  |

| 1.2.8.  | Dynamische MOS-Speicherzelle                                           | 20 |  |  |

| 1.2.9.  | CCD-Speicherzelle                                                      | 21 |  |  |

| 1.2.10. | I <sup>2</sup> L-Schaltkreietechnik                                    | 21 |  |  |

| 1.2.11. | Vergleich der wichtigsten Schaltkreistechniken                         | 23 |  |  |

| 1.3.    | Entwicklungstendenzen und Grenzen der Si-Halb-                         | 23 |  |  |

|         | leitertechnik                                                          |    |  |  |

| 1.3.1.  | Entwicklung des Integrationsgrades im Prognose-                        | 25 |  |  |

|         | zeitraum bis 1985/90                                                   |    |  |  |

| 1.3.2.  | Perspektivische Entwicklungstendenzen der Si-                          | 27 |  |  |

|         | Halbleitertechnik und ihre Grenzen                                     |    |  |  |

| 1.4.    | Wertung der Mikroelektronik                                            | 30 |  |  |

| 2.     | Aufbau und Funktion mikroelektronischer Schalt- | 32  |  |

|--------|-------------------------------------------------|-----|--|

|        | kreise                                          |     |  |

| 2.1.   | Mikroprozessoren                                | 33  |  |

| 2.1.1. | Mikroprozessor FW Erfurt U808D                  | 34  |  |

| 2.1.2. | •                                               | 56  |  |

| 2.1.3. |                                                 | 58  |  |

| 2.1.4. | ·                                               | 61  |  |

| 2.1.5. | Mikroprozessor Zilog Z 80                       | 63  |  |

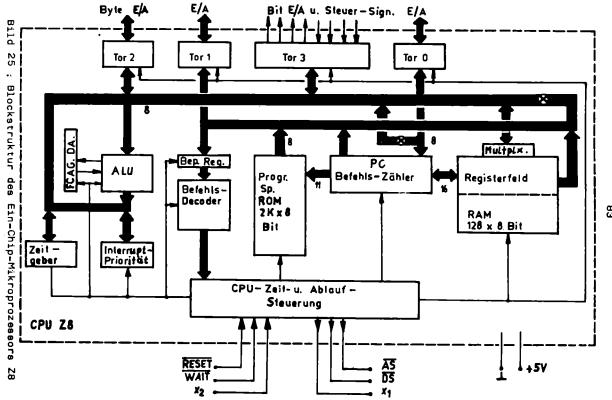

| 2,1.6. | Mikroprozessor Zilog Z 8                        | 75  |  |

| 2.1.7. | Datenvergleich von Mikroprozessoren             | 84  |  |

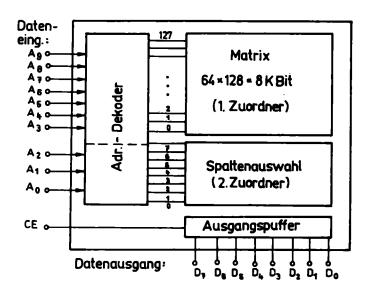

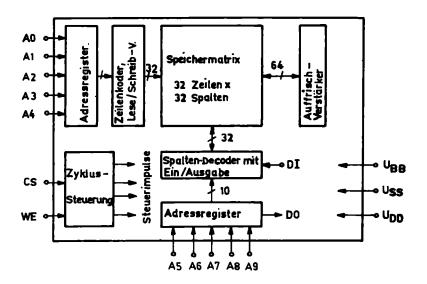

| 2.2.   | Mikroprozeesor-Speicher                         | 86  |  |

| 2.2.1. | ROM*s                                           | 86  |  |

| 2.2.2. | RAM's                                           | 89  |  |

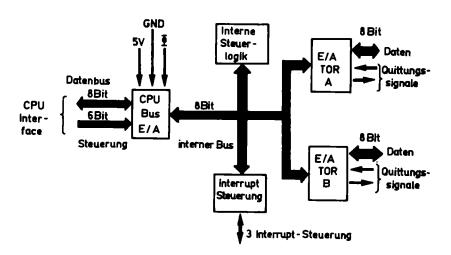

| 2.3.   | Mikroprozessor-E/A-Schaltkreiss                 | 94  |  |

| 2.3.1. | DMA                                             | 94  |  |

| 2,3,2, | USART, SIO                                      | 94  |  |

| 2,3,3. | PPI, PIO                                        | 96  |  |

| 2,3,4, | стс                                             | 97  |  |

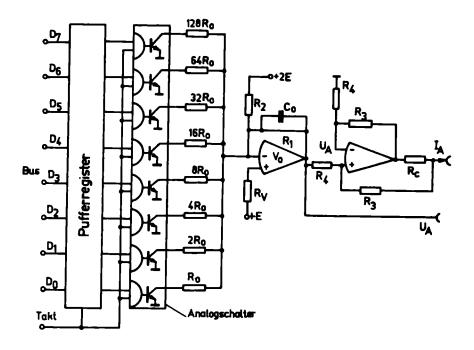

| 2,3,5, | ADC, DAC                                        | 97  |  |

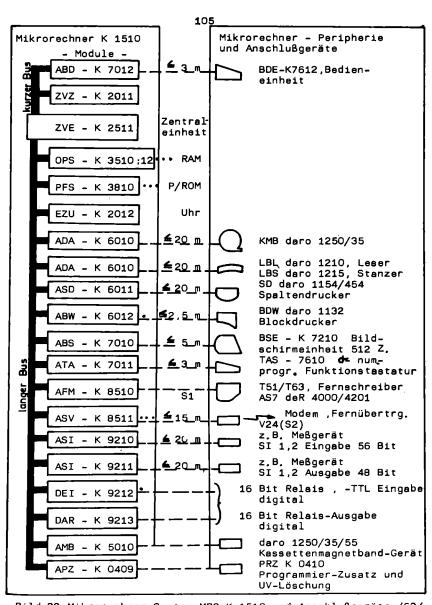

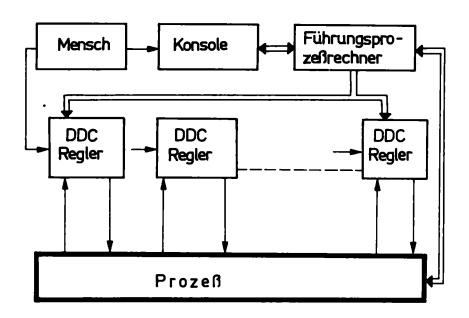

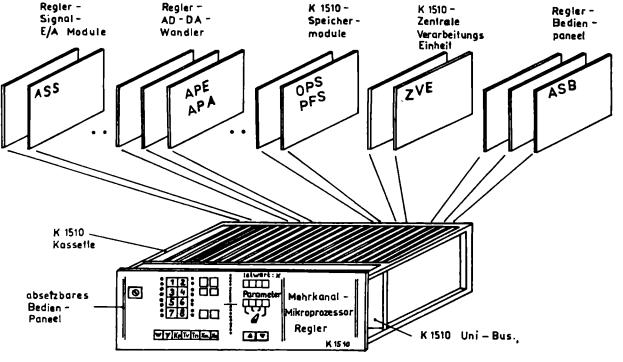

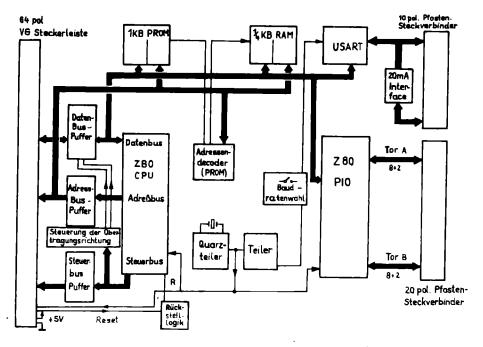

| з.     | Modulares Mikrorechnersystem K 1510             | 104 |  |

| 3.1.   | ZVE - zentrale Verarbeitungseinheit             | 104 |  |

| 3.2.   | ZVZ, ZVE-Zusatzeinheit                          | 107 |  |

| 3.3.   | PFS - Festwertspeicher                          | 107 |  |

| 3.4.   | OPS - Lese-Schreibspeicher                      | 107 |  |

| 3,5,   | Anschlußsteuerungen                             | 107 |  |

| 3.6.   | STM - Stromversorgung                           |     |  |

| 3.7.   | Eingabe-, Bedien- und Anzeige-Einheiten         | 110 |  |

| 3.8.   | Programme zum Mikrorechnersystem K 1510         | 110 |  |

| 4.     | Modulares Mikrorechner-System K 1520            | 113 |  |

| 4.1.   | ZRE - Zentrale Recheneinheit                    | 113 |  |

| 4.2.   | OPS - Operativ-Speicher                         | 113 |  |

| 4.3.   | PFS - Festwertspeicher                          | 114 |  |

| 4.4.   | OFS - Operativ-Festwert-Speicher                | 114 |  |

| 4.5.   | BVE - Buaverstärker                             | 114 |  |

| 4.6. | ADA - Anechlußeteuerung                                                   | 114 |

|------|---------------------------------------------------------------------------|-----|

| 4.7. | BDE - Bedieneinheit                                                       | 115 |

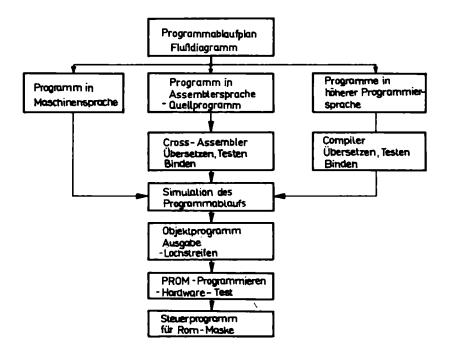

| 5.   | Entwicklungsmethodik von Mikroprozessor-Geräten                           | 117 |

| 5.1. | Mikroprozessor-Programmiersprachen                                        | 118 |

| 5.2. | Assemblieren von Quellprogrammen                                          | 118 |

| 5.3. | Simulation von Mikroprozessor-Programmen                                  | 119 |

| 5.4. | Compilieren von Mikroprozessor-Programmen                                 | 120 |

| 5.5. | Ablauf der Mikroprozessor-Programmierung mit                              | 120 |

|      | Hilfe eines Wirterechners                                                 |     |

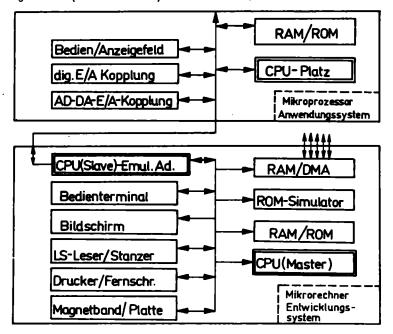

| 5.6. | Mikroprozessor-Geräteentwicklung mit Hilfe                                | 121 |

|      | einee Mikrorechner-Entwicklungssystems                                    |     |

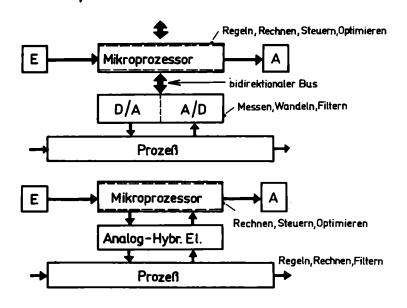

| 6.   | Anwendung von Mikroprozessoren zur Automatieie- rung von Prozeßabläufen   | 125 |

| 6.1. | Allgemeine Mikroprozessor-Anwendungen                                     | 125 |

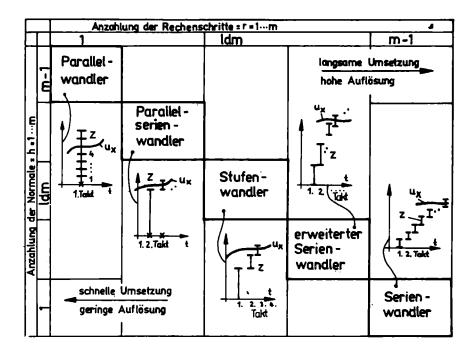

| 6.2. | Mikroprozessor-Prozes-Kopplung zur analogen In-<br>formationsvererbeitung | 128 |

| 6.3. | Entwicklungstendenzen automatisierter Prozesse                            | 132 |

| 7.   | Mikrorechner-Termini der engliechen,                                      | 134 |

|      | russischen und deutschen Sprache                                          |     |

| θ,   | Erklärungen von Begriffen der Mikrorechen-<br>technik                     | 140 |

| 9.   | Literaturverzeichnis                                                      | 148 |

## Mikroprozessoren

### O. Einleitung

Das "intellektuelle" Leistungsvermögen der meisten technischen Prozesse unserer Zeit befindet eich in einem gravierenden Widerspruch zu ihrer mechanischen und energetischen Produktivität. Trotz der stürmischen Entwicklung der technischen Kybernetik mit ihren tragenden Begriffen – messen, steuern, regeln, stellen, registrieren, rechnen, bilanzieren, optimieren, adaptieren und lernen – ist der Anteil der Informationsverarbeitung in technischen Prozessen im Vergleich zu organischen Prozessen sehr gering. Die klassische Automatisierungstechnik beschränkte sich auf wenige Hauptprozesse, da ihre Kosten einen massenhaften Einsatz nicht zuließen. Zudem führten komplexe Automatisierungsaufgaben zu Einrichtungen mit Anlagencharakter von beachtlichen räumlichen und energetischen Dimensionen.

Die Erfindung der Dampfmaschine 1769 durch James Watt kann als Meilenstein der ersten industriallen Revolution bezeichnet werden. Mit ihr zog die technische Energie grundsätzlich in die mechanischen Prozesse ein. Aber diese Energiequelle (Energiewandlung) führte noch nicht zum massenhaften Einsatz der technischen Energie - ihr spezifischer Charakter ließ es nicht zu. Erst mit der Erfindung des elektrodynamischen Prinzips hundert Jahre später, 1866, durch Siemens, wurde mit dem Elektromotor ein Durchbruch erreicht, der die gesamte Technik umfaßte. Der Elektromotor löste die Dampfmaschine nicht nur ab, sondern stimulierte die Schaffung völlig neuer Gebrauchswerte in allen Bereichen der Wirtschaft. In unterschiedlichsten Ausführungsformen ist der Elektromotor heute Bestandteil mannigfaltigster Erzeugnisse. So werden in einem Haushalt gegenwärtig ca. 5 bis 15 Motore verwendet. Mit den klassischen Automatisierungsmitteln, den analogen Regel-, Steuer-, Oberwachungeeinrichtungen und den digitalen Prozeßrechnern hat die technische Information ebenfalls Einzug in die technischen Prozesse gehalten. Sie wurde damit wesentlicher Bestandteil der zweiten industriellen Revolution, der wissenschaftlichtechnischen Revolution.

Ein umfassender Durchbruch in der Anwendung der Informationsverarbeitung wird jedoch erst möglich, wenn eine breite Anpaßfähigkeit, ökonomisch, energetisch und mechanisch gegeben ist. Diese entscheidende Voraussetzung wird von der Informationsverarbeitung auf mikroelektronischer Basis voll erfüllt. Die Mikroelektronik wird damit zu "einer der grundlegenden Seiten der wissenschaft-lich-technischen Revolution" /1/. Sie ermöglicht nicht nur eine Gebrauchswertsteigerung bekannter Erzeugnisse, sondern ganz besonders eine außerordentlich breite Gebrauchswertschöpfung. Mit der Mikroelektronik ist es möglich, neuertige Geräte zu schaffen, in denen stoffliche, energetische und informationelle Prozesse als optimale Einheit gestaltet sind, Geräte einer völlig neuen Qualität. Da sie in erheblichem Maße Denkprozesse des Menschen übernehmen können, werden sie nicht unberechtigt mit dem anspruchsvollen Attribut "intelligent" charakterisiert.

Die Fundamente für die überdurchechnittlich wachsende Leistungefähigkeit der hoch- und ultrahochintegrierten Schaltkreistechnik

der Gegenwart wurden allgemein mit der Herausbildung der Halbleitertechnik Anfang der Fünfziger Jahre und der digitalen Rechentechnik Mitte der Vierziger Jahre gelegt. Die seit 1961 bekannte

Silizium-Transistortechnik ermöglichte eine rasch anwachsende

Schaltungsintegration, so daß es über einfache und mittelintegrierte Schaltkreise 1971 gelang, eine komplette zentrale Verarbeitungseinheit eines Digitalrechners als hochintegrierten

Schaltkreis zu realisieren. Damit wurde eine weltweite Auseinandersetzung zur vorrangigen Weiterentwicklung der Mikroelektronik ausgelöst.

Nach bisherigem Erkenntnisstand wird die Silizium-Halbleitertechnik für mindestens 20 Jahre eine gesicherte, technologisch immer besser beherrschte Methode der Schaltungsintegration sein. Sie wird nach prognostischen Einschätzungen die Leistungsfähigkeit von ca. 25 000 unterschiedlichen Erzeugnissen bestimmen und zu-

gleich Maßetab des wissenschaftlich-technischen Fortschritts unterschiedlichster Wirtschaftszweige werden. Die außerordent-liche internationale Forschungskonzentration auf dem Gebiet der Mikroelektronik wird zu einem entsprechend überdurchschnitt-lichen Erkenntniszuwachs führen, so daß die entscheidenden Merkmale von Erzeugnissen durch die Anwendung der Mikroelektronik bestimmt werden:

Gebrauchswert,

moralische Lebenadauer,

Materialeinsatz,

Energieverbrauch,

Zuverlässigkeit,

Genauigkeit,

Arbeitsproduktivität ihrer Fertigung.

## 1. Technologie und Entwicklungstendenzen elektronischer Schaltkreise

- 1.1. Schaltkreis-Fertigungeprozeß

- 1.1.1. Klassischer Herstellungsprozeß mikroelektronischer Schaltkreise

Die technologischen Herstellungsverfahren /2/ mikroelektronischer Schaltkreise zeichnen sich international einheitlich durch etwa gleichartige Hauptschritte aus. Als Basiematerial dient Silizium:

- Reinigen des polykristallinen Siliziums in Hochfrequenz-Ufen

- Die verbleibende Verunreinigung bestimmt als erste Komponente die Schaltkreisausbeute.

- Kristallwachstum und Erzeugen einer p- oder n-leitenden Dotierung aus einem Schmelzbad von ca. 1 200°C.

- Das Ergebnie ist ein Silizium-Einkristallbarren von 25 ... 150 mm Durchmesser und 150 bis 400 mm Länge.

Kristallversetzungen bilden die zweite Ausfallkomponente.

- Schneiden des Barrene in ca. 0,2 mm dünne Scheiben, Polieren, Läppen und Atzen bie auf eine Rauigkeit von weniger als 0,5 μm.

- Diese ca. 0,1 mm dicken Si-Scheiben bilden das Trägersubstrat der Schaltkreiselemente.

- Epitaxiales Aufwachsen einer einkristallinen Schicht auf der Oberfläche des Si-Kristalles bei gleichzeitigem oder nachfolgendem Passivieren mit Sauerstoff.

- Damit entsteht eine stabile Silizium-Oxid (SiO<sub>2</sub>)-Schicht auf dem Substrat.

- Maskierung der Oberfläche der oxydierten Si-Scheibe mit Hilfe einer photoempfindlichen Schicht und UV-Licht, das durch eine entsprechende Maske (Schablone) auf die Siliziumscheibe projiziert wird.

- . Nach einem Atzvorgang (Säure, Plaema) eind die Stellen freigelegt, an denen die Diffussion mit Fremdatomen erfolgen soll (Gravur).

- \_ Diffussion von entsprechenden p- oder n-leitenden Fremdatomen in die gravierten Zonen (freigesetzte "Fenster").

- Damit ist eine pn (np)-Isolationszone oder ein pn-Obergang einer Diode oder eines Transistors hergestellt.

- Wiederholung der Prozesse Maskieren, Passivieren und Diffundieren je nach Halbleitertechnologie und Kompliziertheit des Schaltkreises.

- Metallieierung der künftigen Kontaktstellen des Schaltkreises für die äußeren Anschlüsse.

- Auf einer Si-Scheibe befinden eich nun kollektiv gefertigt ca. 100 bis 20 000 gleiche Einzeltransistoren oder integrierte Schaltkreise kleinerer Zahl.

- Ritzen und zerteilen der Halbleiterscheibe,

- Je nach Ausbeute (12 ... 25%) erhält man eine enteprechende Anzahl funktionsfähiger "nackter" Halbleiter-Chips.

- Montage der Chips auf Trägermaterial (Gehäuseboden) und Kontaktieren (Bonden) der Chip-Kontaktstellen mit den Anschlußfahnen des künftigen Schaltkreises.

- Hermetische Abdichtung des Schaltkreises nach erfolgtem Wasch-,

Trocknungs- und Prüfprozeß (Verkappen in Metall-, Keramik-,

oder Plastgehäuse).

Die vollständige Herstellungstechnologie ist wesentlich differenzierter und komplizierter. Sie hängt in entscheidendem Maße von der gewählten Halbleitertechnologie ab.

#### 1.1.2. Weiterentwicklung der Fertigungeverfahren (LSI)

Der Obergang vor der mittelintegrierten (MSI) zur hochintegrierten (LSI) Schaltkreistechnik vollzog sich 1970 bis 1972 im wesentlichen auf der Grundlage des klassischen Halbleiter-Fertigungsverfahrens mit den darin enthaltenen charakteristischen Phasen:

- · Herstellen von Si-Scheiben,

- · Herstellen von Fotomasken,

- . Oxydationsprozesse (S102),

- · Fotolithographie (Belichten, Entwickeln, Härten, Ätzen),

- · Diffussionsprozesse (n-, p-Dotierung),

- Verkappen.

Die Forderung nach höheren Integrationagraden (Funktionaelementen pro Schaltkreis) wurde immer mehr durch folgende Faktoren erfüllt:

- · Vergrößerung der Chipfläche eines Schaltkreises,

- Verkleinerung des Flächenbedarfes für eine Halbleiter-Grundstruktur (Linienbreite),

- Verkleinerung der notwendigen Bauelementezahl zur Realisierung eines Funktionselementes (z. B. Speicherzelle, Gatter ...).

Die Vergrößerung der Chipfläche eines Schaltkreises setzt allein eine Vergrößerung der Schaltkreisausbeute, d. h. eine entsprechende Verringerung der Fehlerdichte auf der Si-Scheibe voraus. Es ist bisher nur unzureichend gelungen, das Phänomen der Kristallfehler (Verunreinigung, Kristall-Versetzungen) zu klären. Eine willkürliche Vergrößerung der Chipfläche ist unmittelbar mit einer dratischen Senkung der Ausbeute, d. h. Erhöhung der Chipkosten verbunden. Schwerpunkte der Weiterentwicklung der Halbleiter-Fertigung hochintegrierter Schaltkreise sind:

#### - Elektronenstrahl-Lithographie:

Die Verkleinerung der Halbleiter-Grundstrukturen ist unmittelbar durch das fotolithographische Verfahren begrenzt, so daß sich ein Übergang von der Licht-Foto-Lithographie zur UV-Fotolithographie oder zur Elektronenstrahl-Lithographie vollzieht. Raeter-Elektronenstrahl-Lithographie-Verfahren gestatten dank ihres wesentlich höheren Auflösungsvermögens die Realisierung von Linienbreiten unter 0,3 µm. Darüberhinaus ist eine vollautomatische Strahlsteuerung (Positionierung und Intensität) möglich, so daß Maeken zur Konturübertragung auf die Si-Scheibe in Zukunft überflüssig werden. Die notwendige Programmsteuerung des Strahls übernimmt ein Prozeßrechner.

#### - Ionenimplantation

Die Dotierung des Si-Halbleiterkrietalle mit Fremdatomen läßt sich gegenüber dem allgemeinen Diffussioneprozeß wesentlich genauer beherrschen, wenn das Verfahren der Ionenimplantation (Einpflanzen) verwandt wird. Nach diesem Verfahren werden z. B. Phosphor- oder Borionen auf 40 bis 120 KeV beschleunigt und bei Zimmertemperatur auf den Halbleiter geschossen.

Neben der genauen Dotierung (Selbstjustieren) des Halbleiters wird mit diesem Verfahren eine Verschiebung der Schwellspannung (UT) von MOS-Schaltkreisen erreicht, wodurch eine volle Kompatibilität sowohl der n-Kanal-, als auch der p-Kanal-MOS-Schaltkreise zu Bipolarschaltkreisen erreicht wird. Die meisten Mikroprozessor-Schaltkreise in MOS-Technik sind ionenimplantiert.

#### - Polykristallines Si-Gate (SGT, silicon gate techn.)

Während man bei mittelintegrierten MOS-Schaltkreisen das Gate (Steuerelektrode) aus Metall (Al) herstellt, wird bei hochintegrierten MOS-Schaltkreisen überwiegend polykristallines Silizium, das ebenfalls leitfähig ist, genutzt.

Da zu seiner Bildung aus dem Silizium-Oxyd der Kanalzone keine Maske benötigt wird (selbstjustierend), lassen sich kurze Kanalzonen realisieren. Insgesamt bringt das SGT-Verfahren folgende Vorteile:

- · Verkleinerung der Bauelementeabmessungen,

- Verringerung der Schwellspannung U<sub>T</sub>,

- · Verringerung der parasitären Kapazitäten,

- Erhöhung der Bauelemente-Zuverlässigkeit.

1.2. Schaltungstechnische Elemente mikroelektronischer Schaltkreise

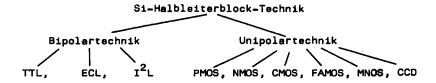

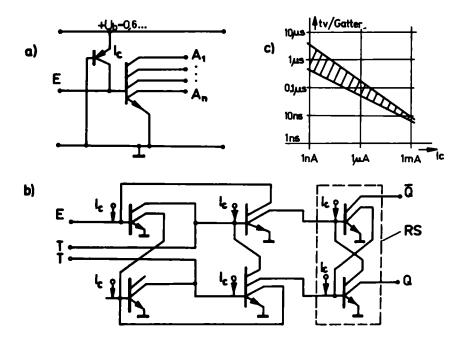

Hochintegrierte mikroelektronische Schaltkreise sind bisher nur auf der Basis binärdigitaler Gatter- und Speicherschaltungen re- alisiert. Ihre Funktion ist rein elektronisch, Ein Übergang zu hochintegrierten analogen Schaltkreisen und zur Funktionalelektronik (Optoelektronik, Mikroakustik ...) /6/ ist zukunftsträchtig, jedoch noch nicht beherrscht. Dominierend sind weit ausgebaute, hochleistungsfähige Schaltungskonzepte der MOS- und Bipolar-Siliziumtechnik (Bild 1). Ihre Möglichkeiten sind bei weitem noch nicht ausgeschöpft.

Bild 1: Wichtige Halbleiter-Schaltkreistechniken zur Schaltkreisintegration

Eine Reduktion der Anzahl der in Bild 1 angegebenen Techniken ist zu erwarten, jedoch ergeben sich so markante Unterschiede in den Gesamtschaltkreiseigenschaften, daß mehrere Konzepte dominieren werden:

Bipolar: I<sup>2</sup>L, TTL

Unipolar: NMOS, CMOS, MNOS, CCD

Traditionelle Schaltkreisfamilien wie DTL, DCTL, RCTL, RTL, DZTL verlieren völlig ihre Bedeutung.

#### 1.2.1. TTL (transistor-transistor-logic) - Schaltkreise

Transistor-Transistor-Logik-Schaltkreise /7/, /8/, bilden in der MSI (medium scale integration, Mittelintegration) mit ca. 40% Anteil die wichtigste Schaltkreisklasse. Mit ihrer Betriebs-

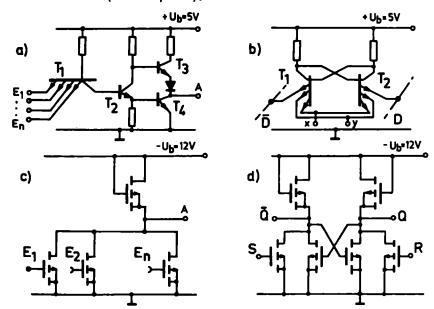

spennung von +5 V haben sie eich zur Schaltkreisnorm entwickelt. In MSI-Technik existiert in allen Industrieländern ein umfassendes Sortiment an Gattern, Speichern, Registern, Kodierern, Dekodierern, Zählern, Multiplexern, Treiberschaltkreisen usw. Die TTL-Technik besitzt auch künftig neben der LSI (Large ecale integration, Großintegration) als Ergänzungsschaltkreise volle Bedeutung. Bild 2 a) zeigt ein 4-fach-NAND-Gatter und Bild 2 b) ein Flip-Flop als Zelle eines Matrixapeichers. Charakteriatisch sind die Multiemitter-Eingänge. Liegt an einem der Eingänge "O" an, so ist der enteprechende Transistor leitend. Daraus folgen die Schaltzustände aller weiteren Transistoren. Versionen der Standard-TTL-Technik sind die leistungsarme (low power) TTL-Technik und die Hochgeschwindigkeits-TTL-Technik. Eine wesentliche Steigerung der Arbeitsgeschwindigkeit der TTL-Technik wird erreicht, wenn der Sättigungszustand der Schalttransistoren durch Schottky-Dioden verhindert wird (Schottky-TTL).

Bild 2: Klassische Bipolar- und MOS-Schaltkreiselemente

- a) TTL-NAND-Gatter

- b) TTL-Speicherzelle

- c) PMOS-NOR-Gatter

- d) PMOS-RS-Flip-Flop

#### 1.2.2. PMOS (p-metal oxide semiconductor)- Schaltkreise

Die p-Kanal-selbstsperrende-MOS-Feldeffekt-Transistor-Technik /8/mit hohen Betriebsspannungen von - $\mathbf{U}_b$  bis zu 30 V ist strukturell und technologisch die einfachste Transistor-Schaltkreistechnik. Mit der großen Schwellspannung zur Üffnung des Drain-Source-Kanals von - $\mathbf{U}_T$  = 3,5 ... 5 V besitzt sie eine hohe Störsicherheit. Der geringe Platzbedarf pro Transistorfunktion und die kleine Anzahl technologischer Schritte führten dazu, daß die ersten hochintegrierten Schaltkreise in PMOS-Technik realisiert wurden. Die Funktion des PMOS-NOR-Gatters folgt aus Bild 2 c). Liegt an einem der Eingänge  $\mathbf{E}_1$  ...  $\mathbf{E}_n$  ein hinreichend negatives Signal an, so wird der entsprechende Transistor leitend, wodurch das Ausgangseignal von seinem L-Pegel (- $\mathbf{U}_b$ ) auf logisch Null geht. Damit wird die NOR-Funktion realisiert.

Bild 2 d) zeigt ein RS-Flip-Flop. Nimmt der Setz-Eingang S des  $-U_b$ -Potential an (=L,low), so wird der angesteuerte Transistor leitend. Von seinem Drain wird dieser Nullzustand (=O) zum Nachbarn der kreuzgekoppelten Transistoren übertragen, wodurch dieser sperrt. Damit wird das Ausgangssignal Q = L gesetzt. Das Rücksetzen erfolgt gespiegelt durch R = L. Der eingespeicherte Zustand bleibt statisch erhalten, er geht jedoch verloren, wenn die Betriebsspannung ausgeschaltet wird.

Der wichtigste Nachteil der PMOS-Technik ist die relativ geringe Arbeitsgeschwindigkeit mit ca. 300 ns Schaltzeiten. Sie folgt unmittelbar aus der Löcherleitung des p-leitenden Kanals und der Hochohmigkeit selbstsperrender Transistoren.

#### 1.2.3. NMOS (n-metal oxide semiconductor) - Schaltkreise

Ohne zusätzliche Maßnahmen führt die n-Kanal-MOS-Technik unmittelbar auf selbstleitende Transistoren, da positive Ladungen im Gate-Isolator (SiO<sub>2</sub>) bereits ohne äußere Gatespannung einen n-Kanal influenzieren, wodurch diese Transistoren relativ niederohmig sind /13/.

Darüberhinaus führt die Elektronen-Leitfähigkeit zum echnellen Ladungsträgertrensport. Für NMOS-Schaltkreise eind im allgemeinen negative Vorspannungen bereitzustellen, wenn diese entsprechend gesperrt werden sollen. In verschiedenen hochintegrierten

Schaltkreisen wird die Vorspannung aus der +5 V Versorgungsspannung intern erzeugt.

weeentlich günstiger ist jedoch das Verfahren, mit Hilfe der Ionenimplantation die Schwellspannung U<sub>T</sub> so festzulegen, daß unmittelbar TTL-Kompatibilität entsteht. Um volle TTL-Kompatibilität zu erreichen, ist neben der notwendigen Umschaltspannung von 1,5 ... 2 V auch eine erhöhte Stromergiebigkeit der Ausgangsstufen zu garantieren. Diese Anforderungen werden von der NMOS-Transistortechnik erfüllt. Sie gehört damit zur bestimmenden Technologie bei der Herstellung hochintegrierter Schaltkreise.

#### 1.2.4. CMOS - Schaltkreise

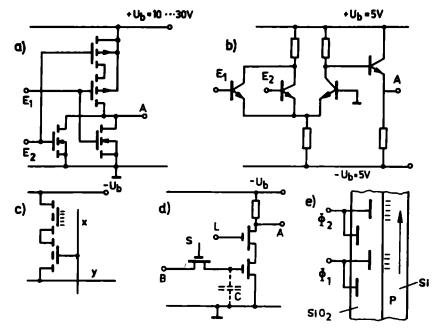

Mit der Komplementär-MOS-Transistor-Technik kann gesichert werden, daß der Ruhestromverbrauch der Schaltkreise unabhängig von ihrem logischen Zustand nur noch durch Restströme bestimmt ist. Wie Bild 3 a) zeigt, ist bei einem leitenden unteren Transistor (n-Kanal) stets ein oberer Transistor gesperrt (p-Kanal). Damit wird nur Strom benötigt, um im dynamischen Umschaltzustand die parasitären Kapazitäten umzuladen.

Bei Ausgangs-Signaländerungen von O nach +U<sub>b</sub> liefern die oberen Transistoren und von +U<sub>b</sub> nach O mindestens ein unterer Transistor den Umladestrom. Da stets ein Transistor leitend ist, ergeben sich kurze Umladezeiten von weniger als 100 ns. Durch den extrem geringen Leistungsbedarf der CMOS-Schaltkreise lassen sich sehr effektive Lösungen für Geräte mit Batteriebetrieb realisieren. Darüber hinaus besitzen sie auf Grund der komplementären Schaltzustände einen optimalen Störabetand, so daß sie für industrielle Einsatz-fälle besonders gut geeignet sind.

Bild 3: Spezielle Schaltkreiselemente der integrierten Technik

- a) CMOS-NOR-Gatter

- b) ECL-OR-Gatter

- c) Floating-Gate-MOS-Speicher-Zelle

- d) dynamische MOS-Speicherzelle

- e) CCD-MOS-Speicherelement

## 1.2.5. ECL (emitter coupled transistor Pogic)-Schaltkreise

Während alle anderen digitalen Schaltkreistechniken die Schalttransistoren vom gesperrten in einen vollständig gesättigten Zustand umschalten, sind die Transistoren in der ECL-Technik nicht gesättigt, sondern im linearen Arbeitsbereich.

Damit wird die kürzeste Umschaltzeit der Transistortechnik überhaupt erreicht.

Bild 3 b) zeigt ein ECL-OR-Gatter. Der Emitterwiderstand zur negativen Betriebespannung - $\mathbf{U}_{b}$  bestimmt den maximalen Arbeits-punktstrom. Unabhängig von den Signalzuständen an den Eingängen  $\mathbf{E}_{1}$ ,  $\mathbf{E}_{2}$  ist einer der drei Transistoren mit diesem Arbeitspunktstrom leitend.

In hochintegrierten Schaltkreisen wird die ECL-Technik nur verwendet, wenn höchste Arbeitageschwindigkeiten erforderlich eind.

1.2.6. FAMOS-Speicherzelle (floating gate avalanche-injection MOS)

Mit dem FAMOS-Feldeffekttraneistor ist eine zerstörungsfreie Speicherzelle realisierbar /8/. Die Anordnung entspricht der Schaltung nach Bild 3 c). Das Gate des oberen Transistore ist vollständig in einer isolierenden SiO<sub>2</sub>-Schicht "schwimmend" eingebettet. Durch Überwinden der Drain-Substrat-Durchbruchepannung (Avalancheeffekt) mit Hilfe relativ großer Spannungen (-30 ... -50 V) lassen sich in einer Einschreibzeit von ca. 1 ms Ladungeträger auf des Gate transportieren.

Damit ist die Zelle programmiert.

Die Löschung des Speicherinhaltes erfolgt durch UV-Licht-Bestrahlung. Die Ladungsträger aller Speicherzellen des Schaltkreises fließen dann zum Substrat ab. Da die Ladungsspeicherung auf dem isolierten Gate betriebsspannungsunabhängig ist, bleibt der Speicherinhalt auch bei Versorgungsspannungsausfall erhalten.

Diese Speicherzelle besitzt für elektrisch programmierbare Nur-Lese-Speicher (EPROM) in der hochintegrierten Technik eine grundlegende Bedeutung. Die Speicherzeit beträgt mehrere Jahrzehnte.

#### 1.2.7. MNOS-Speicherzelle (metal nitride oxide semiconductor)

Die Grundanordnung der MNOS-Speicherzelle entspricht der FAMOS-Schaltung nach Bild 3 c) /8/. Jedoch besitzt das Gate des oberen Transistors einen äußeren Anschluß, der es ermöglicht, auf elektrischem Wege Ladungsträger in das Dielektrikum zwiechen Gate und Substrat zu bringen und wieder zu entfernen. Das Dielektrikum ist im Unterschied zum FAMOS-Transistor nicht nur ein einziger Isolator, sondern besteht aus  ${\rm Si_3N_4-SiO_2-Grenzschichten}$ , die Haftstellen für eine stabile Ladungsträgerspeicherung (Tage, Monate, Jahre) besitzen. Wird eine entsprechend hohe negative Spannung an das Gate gelegt, werden diese Haftstellen positiv geladen Nach Entfernen der Gatespannung bleiben die positiven Ladungen haften, womit die Zelle programmiert ist.

Ein Betriebespannungsausfall kann auch hier den Speicherzustand nicht ändern. Der Umspeicherzustand ist ca. eine Million mal wiederholbar. Danach treten Ermüdungserscheinungen auf. Für die hochintegrierte Schaltungstechnik, insbesondere in der Automatisierungstechnik, ist die MNOS-Speicherzelle eine praktiech unentbehrliche Lösung zur Programm- und Datensicherung.

#### 1.2.8. Dynamische MOS-Speicherzelle

Für die Speicherung mittlerer Datenmengen bei kurzen Zugriffezeiten sind Speicherzellen mit geringem schaltungstechnischen Aufwand notwendig. Bild 3 d) zeigt eine 3-Transistor-dynamische-Speicherzelle mit MOS-Transistoren. Mit einem Impuls an der Schreibelektrode S wird der Zustand der Bit-Leitung B in den Kondensator C gespeichert. Durch einen Impuls auf der Leseleitung L wird der Speicherzustand des Kondensators gelesen. Da die Speicherfähigkeit des Kondensators (ca. 1 pF) nur gering ist, muß die Kondensatorladung periodisch aufgefrischt werden (nach 1 ms). Das geschieht durch Auffrischverstärker, die die gespeicherte Information des Ausganges A messen, verstärken und in B wieder eingeben.

Die einfachste dynamische Speicherzelle besteht aus einem einzigen MOS-Transistor. Der Gesamtspeicherablauf erfordert eine zwei- oder vier-Phasen-Steuerung zum Informationstransport.

#### 1.2.9. CCD-Speicherzelle (charche coupled devices)

Die ladungsgekoppelte Speicherzelle nutzt die Möglichkeit, an Halbleiter-Oberflächen (z. B. p-dotiertes Silizium) Ladungs-träger kurzzeitig zu speichern /8/, /10/. Zwischen nacheinander angeordneten Gate-Elektroden und dem Halbleiter befindet sich der Isolator SiO<sub>2</sub> (Bild 3 e). Werden an die Gate-Elektroden Potentiale unterschiedlicher Amplitude gelegt, so bestimmen drei Potentiale die Transportrichtung der Ladungsträger. In der Anordnung nach Bild 3 e) werden Zwei-Phasensignale angelegt, wobei eine weitere Potentialstufung durch die unterschiedliche Anordnung der Elektroden erzeugt wird.

CCD-Elemente besitzen einen Aufbau mit sehr kleinen Abmessungen, so daß Datenspeicher mit der größten Speicherkapazität auf Halb-leiterbasie erzeugt werden können. Ihnen wird in der Datenverarbeitungstechnik ein breiter Einsatz zugerechnet.

## 1.2.10. I<sup>2</sup>L-Schaltkreistechnik (integrated injection logik)

Nach dem beträchtlichen Vorsprung, den die PMOS und NMOS-Technik in der hochintegrierten Schaltungstechnik erreicht hatte, gelang as mit der I<sup>2</sup>L-Technik /9/ auf der Basis von Bipolartransistoren, bemerkenswert einfache und unterschiedlichen Belangen anpaßfähige schaltungstechnische Lösungen zu finden.

Bild 4 a) zeigt das logische Grundelement mit einem pnp-Lateral-Transistor als Ladungsträgerinjektor der Basis des Multikollektor-Transistors. Damit ist dieser bei offenem Eingang (E  $^{\rm a}$  L) mit allen seinen Kollektoren in Sättigung. Erst wenn der Injektionsetrom I $_{\rm C}$  durch einen vorhergehenden Schaltkreis übernommen wird, geht er in den Sperrzustand.

Bild 4: I<sup>2</sup>L-Schaltkreistechnik

- a) I<sup>2</sup>L-OR-Gatter

- b) I<sup>2</sup>L-Master-Slave-Flip-Flop

- c) Schaltverzögerung t $_{\rm V}$  als Funktion des Injektionsstromes I $_{\rm C}$

Im Gegensatz zu allen bisherigen Schaltkreisfamilien erfolgt die logische Verknüpfung nicht am Eingang, sondern am Ausgang des Schaltkreises. Diese Verfahrensweise entspricht dem Leitungs-ODER (Wire OR) von Schaltkreisen mit offenem Kollektor. Die Zusammenschaltungsart ist am Master-Slave-Flip-Flop, Bild 4 b) gezeigt. Am Ausgang dieses Flip-Flops ist eine RS-Zelle besonders hervorgehoben. Ein wesentlicher Vorteil der I<sup>2</sup>L-Technik besteht in der in weiten Grenzen anpaßfähigen Veränderung des Kollektorstromes I, und die sich daraus ergebende Gatter-

verzögerungszeit  $t_{_{

m V}}$  (Bild 4 c).

Die logischen Schaltpegel sind durch den Basis-Emitter-pn-Obergang des npn-Multikollektor-Transistors auf 0,5 ... 0,7 V festgelegt. Die hohe Packungedichte und der geringe Energiebedarf einerseits, die hohe Arbeitsgeschwindigkeit gegenüber der MOS-Technik andererseits prädestinieren diese Schaltkreistechnik zur universellsten hochintegrierten Schaltungstechnik.

#### 1.2.11. Vergleich der wichtigsten Schaltkreistechniken

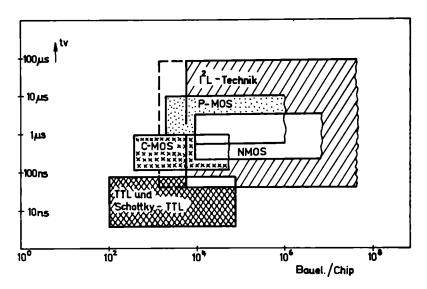

Im Bild 5 ist ein Vergleich der Leietungsfähigkeit wichtiger Schaltkreistechniken gegeben. Die Einordnung erfolgte nach den für die hochintegrierte Schaltungstechnik wichtigsten Kenngrößen: Bauelementezahl pro Chip und die Gatter-Schaltverzögerung t<sub>v</sub>. Dabei wird der universelle Charakter der I<sup>2</sup>L-Technik deutlich.

Ein Zahlenvergleich typischer Parameter der Schaltkreisfunktion und -technologie /11/ veranschaulicht die Vorteile der I<sup>2</sup>L-Technik (Bild 6).

#### 1.3. Entwicklungstendenzen und Grenzen der Si-Halbleitertechnik

Auf die Weiterentwicklung der integrierten Schaltungstechnik wirken zur Zeit zahlreiche stimulierende Faktoren:

- hoher Stand des bereits erreichten technologischen Niveaus der Si-Halbleitertechnik,

- große Investitionen auf dem Gebiet der Halbleiter-Fertigungstechnik und Halbleiter-Prüftechnik,

- hochqualifiziertes Arbeitskräftepotential,

- weitgehende Rohstoffunabhängigkeit der Halbleiterfertigung

Bild 5: Gatter-Schaltverzögerung  $\mathbf{t}_{\mathbf{V}}$  in Zuordnung zur Bauelementezahl pro Chip hochintegrierter Schaltkreise

| NAND 4-fach            | Einheit                          | TTL | CMOS | PMOS | NMOS | I <sup>2</sup> L |

|------------------------|----------------------------------|-----|------|------|------|------------------|

| Fläche                 | 10 <sup>-3</sup> mm <sup>2</sup> | 34  | 32   | 7    | 4    | 3                |

| Masken                 |                                  | 7   | 6    | 4    | 7    | 4                |

| Verlust-<br>leistung   | mW                               | 2   | 0,1  | 0,2  | 0,2  | 0,07             |

| Schaltver-<br>zögerung | ns                               | 10  | 25   | 1000 | 10   | 50               |

Bild 6: Vergleich typischer Parameter aktueller Halbleitertechnologien /11/

- große Erwartungen in der weiteren erfolgreichen Beherrechbarkeit der Si-Halbleitertechnik,

- beachtliches Erkenntnispotential in der theoretischen Erforschung der Halbleiterphysik und Halbleitertechnologie,

- große Erwartungen in den volkswirtschaftlichen Effekten der Informationsverarbeitung auf der Basis hochintegrierter Schaltkreise für eine sehr große Zahl von Erzeugnissen.

Diese Faktoren bewirken eine weltweite Konzentration der theoretiechen, technischen und technologischen Forschung auf dem Gebiet der Mikroelektronik.

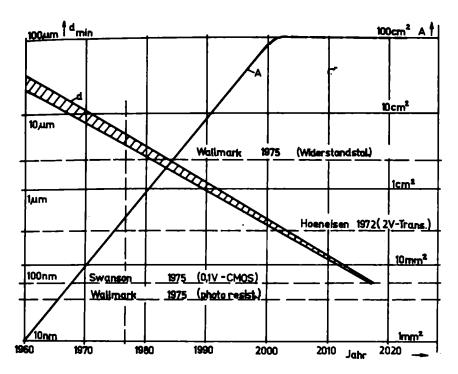

1.3.1. Entwicklung des Integrationsgrades im Prognosezeitraum bis 1985/90

Der Integrationsgrad eines integrierten Schaltkreises wird durch die Anzahl der Transistorfunktionen je Chip bestimmt /5/. Er ist damit durch drei entscheidende Faktoren festgelegt:

- Fläche A des Halbleiterchips,

- Flächenbedarf je Bauelement,

- Anzahl der Bauelemente, die zu einer vollständigen Transistorfunktion benötigt werden.

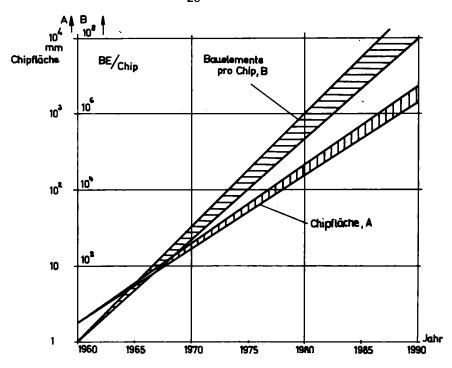

Durch eine systematische Erhöhung der Güte (Reinheitsgrad, Versetzungsfreiheit) des Siliziums und der technologischen Beherrschung des Fertigungsprozesses wird die Anzahl der Fehlstellen auf der Siliziumscheibe wesentlich gesenkt. Zur Zeit gebräuchliche Siliziumscheiben haben Durchmesser von 36 ... 100 mm (Fertigung), 120 ... 150 mm (Labor). Das entspricht Gesamtflächen von ca. 4 000 bis 70 000 mm². Die optimale Chipfläche folgt aus den Kosten für das Silizium, den Scheibenprozeß und die Montage /14/. Insbesondere die Ausbeute steht der Ausnutzung der gesamten Scheibenfläche durch ein einziges Chip im Wege. Die prognostizierte Entwicklung der Chipfläche A ist im Bild 7 gezeigt /12/.

Bild 7: Chipfläche A und Bauelementezahl B pro Chip im Prognosezeitraum 1985/90 /12/

Die Vergrößerung der Anzahl der Bauelemente pro Chip (Bild 7) folgt dem Anliegen, komplexe Funktionen wie Speicher und Rechner in einem einzigen Schaltkreis unterzubringen. Damit wird der Gebrauchswert des Schaltkreises qualitativ gesteigert, Montagekosten werden verringert und die Zuverlässigkeit hochkomplizierter Schaltungen systematisch gesteigert. Der höchste Integrationsgrad ist zur Zeit mit 90 000 Transistorfunktionen in einem CCD-Speicher erreicht /6/. Aus Bild 7 folgt, daß um 1980 die für die Schaltungstechnik außerordentlich große Zahl von 1 Mio Bauelementen pro Chip möglich wird und für 1990 die 100 Mio-Grenze überschritten werden kann.

Für die Speichertechnik ohne kritische Zugriffezeiten ist eine aolche Zahl von Bauelementen nicht übermäßig groß, da die Datenverarbeitung mit Magnetband oder Magnetplattenspeichern über eine Mrd Bit pro Speichereinrichtung verfügt. Der qualitative Unterschied besteht jedoch darin, daß diese Bauelementekapazität im Vergleich zu den genannten Speichermedien in außerordentlich freizügiger Weise strukturiert werden kann.

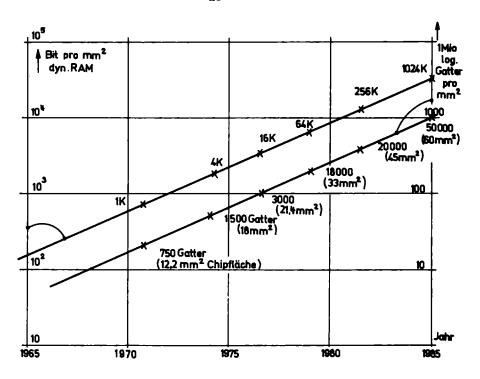

Damit ist die Anwendbarkeit von Schaltkreisen mit über 100 Mio Bauelementen pro Chip ein neues, grundsätzliches Gebrauchswert-problem. Die Nutzung als Daten- und Programmspeicher kann als gesichert angesehen werden. Die Nutzung als produktive informationsverarbeitende Elemente gestattet jedoch die Schöpfung völlig neuer Gebrauchswerte von außerordentlich hoher Qualität. Hier liegt das entscheidende Feld der Möglichkeiten der Mikroelektronik. Bild 8 zeigt das international realisierte und prognostizierte Angebot hochintegrierter Speicherschaltkreise /16/. Danach stehen 1985 Schaltkreise mit 1 Mega-Bit Speicherkapazität zur Vergügung.

Die im Bild 8 angegebene Schaltkreisentwicklung nutzt bereits die Ablösung der Fotolithographie durch die Elektronenstrahllithographie und die Ablösung der klassischen Diffusionstechnik durch Ionenimplantation.

1.3.2. Perspektivische Entwicklungstendenzen der Si-Halbleitertechnik und ihre Grenzen

Für die technologisch wahrscheinliche Ausschöpfung der Möglichkeiten der Silizium-Halbleiterblocktechnik in den wichtigsten

Parametern und Leistungskenngrößen ist es notwendig, einen perspektivischen Zeitraum bis zu den Jahren 2000/2010 zu betrachten.

Eine grundlegende Ablösung der bisherigen Halbleitertechnik ist

nicht zu erwarten, da der halbleitertechnologische Vorlauf die

derzeitigen Strukturvorstellungen der Anwender wesentlich übersteigt /4/, /6/. Nach /5/ wird die sihnvolle maximale Chipfläche A etwa im Jahre 2005 mit 100cm<sup>2</sup> erreicht (Bild 9).

Bild 8: Entwicklung der Speicherkapazität dyn, Speicherschaltkreise im Prognosezeitraum bis 1985 /16/

Damit würde z. B. eine existierende Silizium-Scheibe von 36 mm Durchmesser als runde Ein-Chip-Scheibe unzerteilt verwendet. Um bei einer einnvollen Scheibenausbeute von 10% zu bleiben, müßte jede 10. Scheibe fehlerfrei arbeiten, wobei der derzeit übliche nichtredundante Schaltungsentwurf zugrundegelegt wird.

Bei der Einschätzung der minimalen Strukturabmessungen muß eine Vielzahl von Einflußfaktoren erfaßt werden, so daß sich je nach Halbleitertechnologie, Schaltungstechnik und Fertigungstechnologie unterschiedliche Grenzen ergeben /5/, /6/ (Bild 9).

Bild 9: Entwicklung der Chipfläche A und der minimalen Strichbreite d bei hochintegrierten Schaltkreisen /5/

Bis zum Jahre 1980 gelten Strichbreiten von 1 µm als technologisch beherrschbar, da sie labormäßig bereits realieiert sind. Die Fertigung kleinerer Strichbreiten als 1 µm ist mit Hilfe der Raster-Elektronenstrahl-Mikroskopie und der Ablösung materieller Masken grundsätzlich möglich, da der Elektronenstrahl mit einem Durchmesser von 0,2 nm gegenüber der Wellenlänge des Lichtes ein hinreichendes Auflösungsvermögen besitzt /16/. Die elektronisch bedingte kleinste Strichbreite wird in /17/, /18/ mit 50 und 30 nm angegeben. Jedoch kann sie nicht vor dem Jahre 2010 erreicht werden. Nach /6/ erscheinen Strichbreiten von 0,1 µm mit Hilfe der Elektronenstrahl-Lithographie bereits nach 1980 als realisierbar.

In Bild 10 ist der Stand der Technik 1976 (Spitzenleistungen) mit den elektronisch-technologischen Grenzen in Vergleich gesetzt /3/. Die minimale Größe von Einzeltransistoren und die maximale Integrationedichte orientieren eich an klassischen Schaltungskonzepten der binären digitalen Schaltkreistechnik (Transistor- und Gatterfunktionen).

| Merkmale                                            | Stand der<br>Technik 1976              | techn.<br>Grenzen                               |  |

|-----------------------------------------------------|----------------------------------------|-------------------------------------------------|--|

| minimale Größe von<br>Einzeltransistoren            | 1 000 µm²                              | 1 µm²                                           |  |

| maximale Integrations-<br>dichte                    | 10 <sup>4</sup> Gatter/cm <sup>2</sup> | 2,5 · 10 <sup>7</sup><br>Gatter/cm <sup>2</sup> |  |

| minimale Schaltzeit<br>- absolute Laufzeit -        | 0,2 ns                                 | 1 ps                                            |  |

| minimale Schaltzeit<br>- thermiach begrenzt -       | 1 ns                                   | 10 ps                                           |  |

| max. Taktfrequenz<br>- synchr. NW -                 | 30 MHz                                 | 3 GHz                                           |  |

| min. Verzögerungszeit-<br>Leistungsprodukt          | 10 <sup>-12</sup> Ws                   | 10 <sup>-15</sup> We                            |  |

| min. Speicher-Zugriffs-<br>zeit 10 <sup>4</sup> bit | 10 ns                                  | 0,1 ns                                          |  |

Bild 10: Vergleich wichtiger Kenngrößen integrierter Schaltkreise /3/

#### 1.4. Wertung der Mikroelektronik

Die überragende Leistungsfähigkeit der Si-Halbleitertechnik und -Fertigungstechnologie liegt in folgenden Hauptmerkmalen /4/, /5/, /6/:

- Kollektiver Fertigungsprozeß einer außerordentlichen Anzahl von Funktionselementen.

- . Daraus folgt die hohe Ükonomie des Fertigungsprozesses und die damit ermöglichte Preisdegression dieser Technik.

- Extrem elegante Verknüpfbarkeit (Programmierbarkeit) der einzelnen Funktionselemente zu Gesamtfunktionen.

- Diese Eigenschaft der elektronischen Schaltkreiselemente geetattet eine mit anderen Techniken unvergleichliche Flexibilität der Funktionsanpaseung an nahezu beliebige Aufgabenklassen.

- Hoher und ultrahoher Integrationsgrad von Einzelelementen zu einem einzigen komplexen Funktionselement.

- Das ermöglicht es, nahezu beliebig komplizierte Strukturen der informationsverarbeitenden Technik in einem geschlossenen Fertigungsprozeß herzustellen.

- Hohe Lebensdauer und Verschleißfreiheit der technischen Grundalemente.

- Das ist die entscheidende Grundlage der hohen Zuverlässigkeit und der Wartungsfreiheit, die für hochkomplexe Systeme gefordert werden muß.

- Extrem geringer Energiebedarf des Einzelelementes.

- Die Reduktion des Energiebedarfes pro Schaltkreiselement ist eine wesentliche Realisierungsvoraussetzung für hochkomplexe informationsverarbeitende Geräte.

- ~ Maximale Arbeitsgeschwindigkeit.

- Integrationsgrad und Arbeitageschwindigkeit der Elemente bestimmen die Zugriffszeiten und damit den Datendurcheatz, d. h. die Leistungsfähigkeit der technischen Geräte.

Mit diesen Eigenschaften erweist sich die Mikroelektronik als prädestinierte Technik zur Informationsverarbeitung in nahezu beliebigen Prozessen.

# 2. Aufbau und Funktion mikroelektroni - scher Schaltkreise

Den entscheidenden Durchbruch erreichte die hochintegrierte Schaltkreistechnik mit der Entwicklung des ersten Mikroprozes-sor-Systems MCS 8 /26/ im Jahre 1971, bestehend aus einer Ein-Chip-zentralen Verarbeitungseinheit (CPU, central processor unit) nach dem Vorbild des Prozeßrechners PDP 8, Programmspeichern (ROM, read only memory, Nur-Lese-Speicher) und Datenspeichern (RAM, random access memory, Speicher mit wahlfreiem Zugriff) als Lese-Schreibspeicher.

Im Unterschied zu den integrierten Handrechnern, die im allgemeinen nur ein festgelegtes Repertoire an arithmetischen Rechenfunktionen beinhalten , gestattet der Mikroprozessor eine freizügige Programmierung für unterschiedlichste Aufgaben. Mit 48 elementaren Befehlen ermöglichte er den Aufbau beliebiger Programme, wodurch die qualitativen Merkmale der Universalität von Rechenanlagen grundsätzlich erfüllt wurden. Da der Mikroprozessor nur aus einem Schaltkreis bestand, eröffneten sich ihm epontan außerordentliche breite Einsatzmöglichkeiten. Seit 1971 vollzog eich eine rasche Weiterentwicklung der Mikroprozessortechnik.

Für den Anwender mikroelektronischer Schaltkreise ist der innere Aufbau der Funktionselemente nur so weit von Interesse, als es

- zur Funktionsbeschreibung,

- zur fehlerlosen Zusammenschaltung,

- zum Entwurf der im allgemeinen unumgänglichen Randelektronik und

- zur Erklärung elektronischer Effekte beim Geräteentwurf

notwendig ist.

Innerhalb der firmenspezifischen Schaltkreisfamilien besteht eine lückenlose Kompatibilität für die Zusammenschaltung aller Funktionselemente.

Im allgemeinen werden die Signalbedingungen der TTL-Schaltkreistechnik für alle Ein- und Ausgangspegel zugrunde gelegt. Damit wird zugleich ein breiter Obergang zu den Standard-MSI-Schaltkreisen der TTL-Technik und den dazugehörenden Koppelelementen für systemfremde elektronische Bauelemente (z. B. LED-Display, Relais usw.) gewährleistet.

Auch MOS-Schaltkreise der mittelintegrierten Technik ermöglichen immer mehr die TTL-Anschluß-Kompatibilität.

#### 2.1. Mikroprozessoren

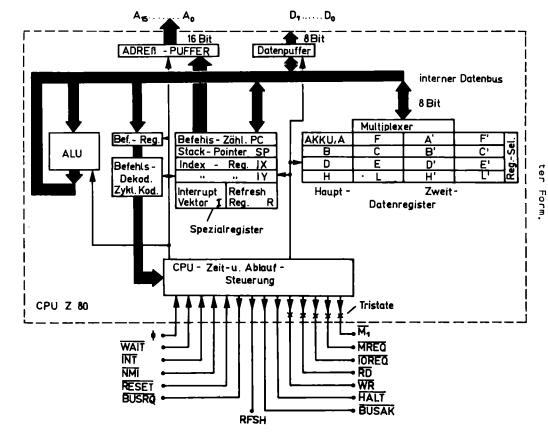

Der Aufbau von Mikroprozessoren ist durch ihre rechentechnische Grundstruktur bestimmt. Im allgemeinen enthält ein Mikroprozessor (CPU) mindestens die Funktionsblöcke:

- Rechenwerk = arithmethisch logische Verknüpfungseinheit

- Steuerwerk = Zeit- und Ablaufsteuerung zur Befehlsabarbeitung und

- Speicher (Register) zur Befehls-, Adressen- und Datenzwischenspeicherung.

Diese Funktionsblöcke erlauben die Abarbeitung einer featgelegten Anzahl von elementaren Befehlen (Instruktionen) in einer durch ein Programm featgelegten Reihenfolge. Zu einem Mikroprozessoraystem gehört neben der CPU eine unterschiedliche Anzahl von Ergünzungsschaltkreisen. Die wichtigsten sind:

RAM's - Lese-Schreibspeicher

ROM's - Festwertspeicher und

E/A - Ein-Ausgabeschaltkreise unterschiedlichster Art.

Ergänzt man Mikroprozessor-Module, bestehend aus den genannten Schaltkreisen, durch Peripherie-Einheiten der Rechentechnik (Tastatur, Anzeige-Displays usw.), so entstehen Mikrorechner. Diese wiederum können zu Mikrorechner-Systemen (Mikrorechner-Anlagen) erweitert werden, wenn ein weiterer Ausbau mit Baueinheiten der Rechentechnik vorgenommen wird (Lochstreifen-Leser,

-Stanzer, Drucker, Magnetbandspeicher usw.). Die Grenzen sind iedoch fließend.

Werden Mikroprozessoren in spezielle Geräte eingebaut - das ist der weitaus häufigere Fall - so spricht man allgemein von mikroprozessorgesteuerten Geräten, speziell z. B. von programmierbaren Waagen, Mikroprozessor-Reglern usw.

2.1.1. Mikroprozessor FW-Erfurt U 808D /18/, /35/, /68/, /71/, /91/, /92/

Der integrierte MOS-Schaltkreis im 18poligen DIL-Plastgehäuse ist eine Zentrale Verarbeitungseinheit (ZVE) in p-Kanal-Silicon. Gate-Technologie für den Aufbau von Mikroprozessor-Geräten und Mikrorechnern.

#### Charakteristische Merkmale sind:

- 8-Bit-Parallel-ZVE auf einem Chip (CPU, central processor unit),

- Basis-Befehlesatz 48 Befehle,

- maximale Taktfrequenz 500 kHz,

- typische Befehlsausführungszeit 20 μs,

- TTL-Kompatibilität (Eingänge und Takt),

- Low-Power-TTL-Kompatibilität (Ausgänge),

- direkt adressierbare Speicherkapazität 16 k-Worte,

- beliebige Erweiterung der Speicherkapazität durch programmunterstützten Speicher-Bank-Betrieb,

- Batufiger 14-Bit-Adressen-Stack-Speicher,

- 7 frei verfügbare Datenregister,

- INTERRUPT-Möglichkeit,

#### a) Außere technische Kennwerte und Eigenschaften

Die nachfolgend angegebenen technischen Kennwerte - Anschlußbelegung, statische und dynamische Daten - beziehen sich auf die 18polige Schaltkreisausführung des U808D /92/. Sie geben lediglich eine kurze Obersichtsinformation

#### - Anechlußbelegung

| Pin | Kurzbez.  | Beechreibung                            |                     |        |  |  |

|-----|-----------|-----------------------------------------|---------------------|--------|--|--|

| 1   | UDD       | Betriebsspannung U <sub>DD</sub> = -9 V |                     |        |  |  |

| 2   | D7        | Datenbus-Ein-/Ausgang 7                 |                     |        |  |  |

| 3   | D6        | Datenbus-Ein/Ausgang 6                  |                     |        |  |  |

| 4   | D5        | -                                       | •                   | 5      |  |  |

| 5   | D4        | •                                       | •                   | 4      |  |  |

| 6   | D3        | •                                       | •                   | 3      |  |  |

| 7   | D2        | -                                       | •                   | 2      |  |  |

| 8   | D1        | Datenbus-Ein-/Ausgang 1                 |                     |        |  |  |

| 9   | DO        | •                                       | •                   | 0      |  |  |

| 10  | Ucc       | Betriebsspann                           | ung U <sub>CC</sub> | ■ +5 V |  |  |

| 11  | S2        | Status-Ausgan                           | g 2                 |        |  |  |

| 12  | <b>S1</b> | Status-Ausgan                           | g <b>1</b>          |        |  |  |

| 13  | so        | Status-Ausgan                           | g O                 |        |  |  |

| 14  | Sy        | Synchron-Aueg                           | ang                 |        |  |  |

| 15  | C2        | Takteingang                             | 2                   |        |  |  |

| 16  | C1        | Takteingang                             | 1                   |        |  |  |

| 17  | RD        | READY-Eingang                           | l                   |        |  |  |

| 18  | IT        | INTERRUPT-Ein                           | gang                |        |  |  |

|     |           |                                         |                     |        |  |  |

#### - Typische statische Kennwerte

Betriebsspannung:  $U_{CC}$  = +5 V  $\pm$  0,25 V Betriebsspannung:  $U_{DD}$  = -9 V  $\pm$  0,45 V

Stromaufnahme:  $I_{DD} = -(I_{CC} + I_{Last}) = -30,...-60 \text{ mA}$

Eingangsspannung: U<sub>eL</sub> = U<sub>DD</sub> ... U<sub>CC</sub> - 4,35 V

$U_{\text{eH}} = U_{\text{CC}} - 1.5 \text{ V} \dots U_{\text{CC}} + 0.3 \text{ V}$

Ausgangespannung:  $U_{aL} = +0.4$  Vmax,  $I_{aL} = 0.4$  mA  $U_{aH} = +2.4$  Vmin,  $I_{aH} = -0.2$  mA

- Typische dynamische Kennwerte

Taktperiode: 2 ... 3 µa

Anstiegs- und Abfallzeit der Eingangseignale: 50 ns

Kapazitäten der Eingangs- und Ausgangs-Anschlüsse: 5 ... 10 pF

/91/, /92/

- Bedeutung der Anschlußbelegung U808D

- D7...DO: Datenbus, bidirektionale Ein-Ausgänge für den Transport allgemeiner Daten zwischen CPU und äußeren Schaltkreisen. Diese Daten können Zahlen, Befehle oder Adressen sein. Das Datenformat ist durch den 8Bit-Bus (ein Byte) festgelegt, so daß z.B. Adressen aus zwei Byte sequentiell gebildet werden.

- . U<sub>CC</sub>, U<sub>DD</sub>: Versorgungsspannungen +5 V und -9 V ohne CPUinternen Masse-Anschluß. Die Teilung der Gesamtspannung von -14 V für den p-Kanal - SGT-MOS-Schaltkreis ermöglicht seine TTL-Kompatibilität.

- .  $C_1$ ,  $C_2$ : Taktaignal-Eingänge (clock input) mit zwei nichtüberdeckenden, phasenverschobenen Taktaignalen der Frequenz  $f_c = 480 \text{ kHz}$ .

- . Sy: Synchronisationstakt:  $f_v = f_c/2 = 240 \text{ kHz}$ .

- .  $S_2$ ,  $S_1$ ,  $S_0$ : Zustandseignale. In Abhängigkeit vom Taktzustand des Prozessors wird eine entsprechende Belegung (O/I) der Signale  $S_2S_1S_0$  (maximal 8 unterscheidbare Taktzustände) nach außen mitgeteilt.

- . RD: Bereitschaftsmeldung (<u>READY</u>) zur Programmfortsetzung in Abhängigkeit von der Peripherie.

- . IT: Unterbrechungsanmeldung (<u>INT</u>ERRUPT)

zur Einleitung eines veränderten Programmablaufs in Abhängigkeit von der Peripherie.

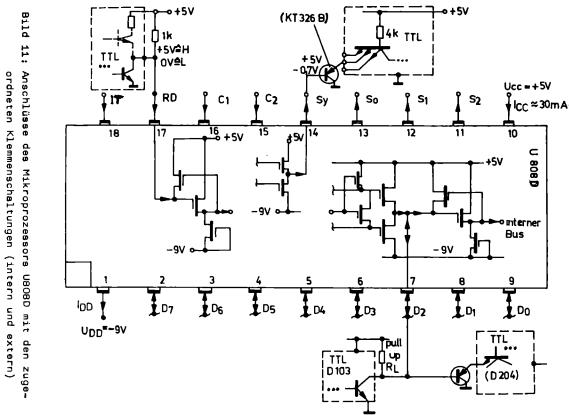

#### - Elektronisches Klemmenverhalten

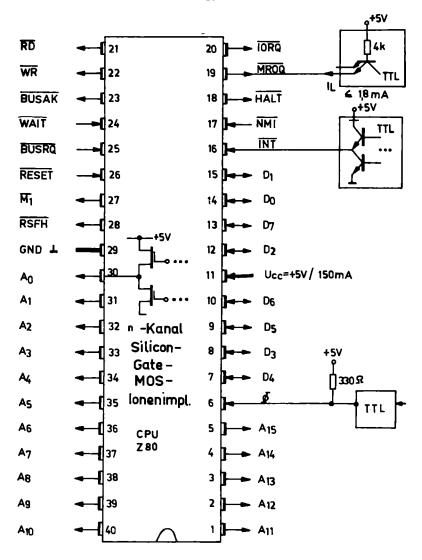

- . Eingangsseitige TTL-Kompatibilität In der Darstellung der CPU nach Bild 11 ist die Bedingung für die TTL-Kompatibilität am IT-Eingang angegeben. Der Treiberwiderstand von 1k dient dem eicheren Erreichen des H (high)-Pegels.

- . Ausgangsseitige TTL-Kompatibilität

Die volle TTL-Kompatibilität zu Standard-TTL-Schaltkreisen läßt sich nur über einen zusätzlichen Ştromverstärkungs-Transistor erreichen (z. B. KT326B).

- . Bidirektionale Bus-Leitungen Um über die gleichen Anschlußklemmen Daten sowohl senden

ale auch empfangen zu können, ist ein Umschalten der Ausgangsklemmen aller an den Datenbus angeschlossenen Schaltkreise in einen neutralen Zuetand möglich (Drei-Zuetanda-Ausgänge, three state outputs). Mit gewissen Einschränkungen kann diese Eigenschaft auch mit Schaltkreisen erreicht werden, die ausgangsseitig offene Kollektoren besitzen (z. B. D103). In beiden Formen ist der Ausgang für den neutralen Zuetand hinreichend hochohmig.

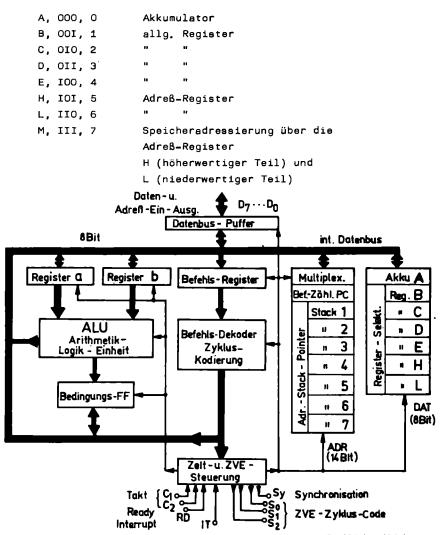

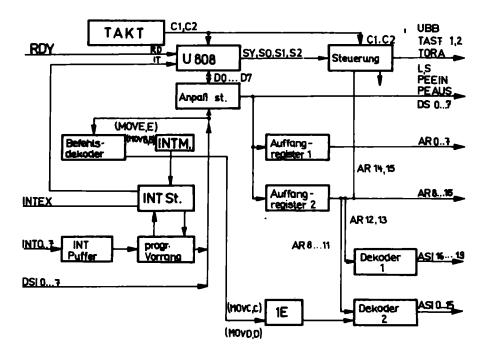

#### b) Innerer Aufbau der CPU/U808D

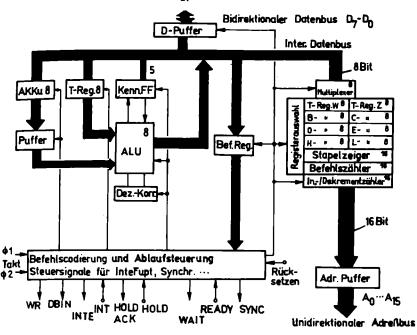

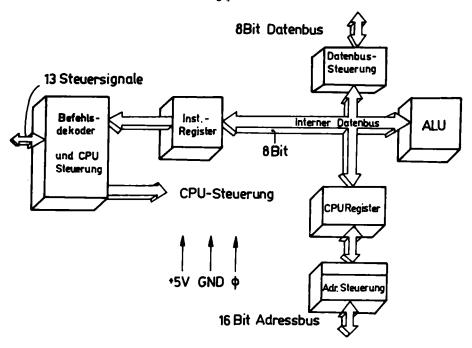

Die Blocketruktur der CPU U808 ist im Bild 12 gezeigt /71/, /91/. Alle Blöcke sind über einen 8-Bit-Datenbus (acht Datenleitungen) so miteinander verbunden, daß sowohl in die Blöcke hinein als auch aus den Blöcken heraus Daten transportiert werden können. Die Tätigkeit jedes Blockes wird über Steuerleitungen eingeleitet und beendet.

Die Blöcke haben folgende Aufgaben:

- Die Zeit- und ZVE-Steuerung setzt den von außen etändig anliegenden Zweiphaeen-Takt  $(C_1, C_2)$  in ein Synchronisationssignal  $(S_y)$  und in drei Maechinenzyklussignale  $(S_0, S_1, S_2)$  um. Damit kann ein Maechinenzyklus aus maximal acht Zuständen bestehen. Sie bestimmen in Abhängigkeit vom Bereitschaftssignal READY (RD) und Unterbrechungssignal INTERRUPT (IT) den zeitlichen Ablauf der Befehlsabarbeitung.

- Der <u>Befehlezähler (PC, program counter, Programmzähler)</u> liefert enteprechend dem Zählerstand die Adresse der abzuarbeitenden Befehle. Da eine Adresse max. 14 Bit (für 16 K-Speicherplätze) umfassen kann, muß eie in einen niederwertigen (8-Bit) und einen höherwertigen (6-Bit) Teil zerlegt werden und durch einen Multiplexer in zwei Worten auf den 8-Bit-Daten- und Adreßbus übertragen werden. Die sieben Adreß-Kellerspeicher (Stack) gestatten das Zwischenspeichern von Adressen (14 Bit) nach dem LIFO-Prinzip (last in-first out, zuletzt hinein zuerst hinaus). Im einfachsten Programmablauf wird

der Befehlezähleretand mit der Abarbeitung eines Befehles um 1 oder 2 oder 3 - je nach Befehleart - automatisch erhöht, so daß die Adresse des nachfolgenden Befehls im Befehlezähler bereitsteht. Bei Unterprogrammaufrufen wird die aktuelle Adresse des Unterprogrammes in den Befenlezähler gebracht. Nach Beendigung der Unterprogrammbearbeitung wird mit einem Rückkehrbefehl die zuletzt in den Stack geladene Adresse wieder in den Befehlezähler übertragen, so daß das Hauptprogramm folgerichtig abgearbeitet werden kann. Der Adreß-Stack-Pointer (Zeiger des Adreß-Keller-Speichers) organisiert das interne Umepeichern der im Stack aufgehobenen Adressen. Mit den 7 Stacks lassen eich maximal 7 Rücksprungadressen aufheben. Bei Oberfüllung des Stack geht die zuerst eingeladene Adresse verloren.

Ober den <u>Datenbus-Puffer</u> erfolgt die Obertragung von Adressen oder Daten zu den äußeren Speichern bzw. Ausgabe-Baugruppen oder umgekehrt der Empfang der gelesenen Daten oder Befehle aus den Speichern bzw. den Eingabesinheiten in die CPU.

Befehle gelangen in das <u>Befehleregieter</u> und werden anschließend im <u>Befehlsdekoder</u> entschlüsselt. Die Entschlüsselung wird durch eine Logik vorgenommen, die die funktionellen und zeitlichen Abläufe für die Aberbeitung von 228 elementaren Befehlen (Instruktionen) festlegt, die aus den 48 Basisbefehlen gebildet werden können. Aus dem erkannten Befehl, der abzuarbeiten ist, folgt die entsprechende Zyklussteuerung. Zur Realisierung des Datentransportes, logischer und arithmetischer Befehle wird ein einziges Befehlswort benötigt. Bei Zweiwort-Befehlen ist an den Befehl ein zu verarbeitendes Datenwort gebunden. Für Sprungund Rufoperationen werden Dreiwort-Befehle benötigt.

Aus dem Operationscode eines 8Bit-Wortes können maximal 28 = 256 elementare Befehle unterschieden werden, wovon im Mikroprozessor U808D 228 genutzt werden.

Daten werden in den <u>Akkumulator A</u> oder in die 8-Bit-<u>Register B</u> <u>bis L</u> gebracht. Durch eine Register-Selektion wird ihre unabhängige Verwendbarkeit ermöglicht. Ihre Adressierung ist durch folgenden Code festgelegt:

Bild 12: Blockschaltbild des Mikroprozessors U808D /91/, /92/

Besondere Verwendung finden in den Mikroprozessor-Befehlen die Register:

- . A als Akkumulator Der Akkumulator liefert bei arithmetischen oder logischen Operationen einen der zwei Operanden und hebt das Resultat der Operationen auf.

- . H und L als Adreß-Speicher für die indirekte Adressierung externer Speicherplätze

Der Inhalt der Register L und H ergibt gemeinsam den mit

M (memory) bezeichneten Speicherplatz des externen Speichers.

Dabei enthält L den niederwertigen 8-Bit- und H den höherwertigen 6-Bit-Adreßteil der 14 Bit Adresse. Die verbleibenden 2 Bit sind ohne Bedeutung.

Sämtliche Verknüpfungen zweier Datenworte erfolgen in der arithmetisch-logischen Einheit (ALU).

Zu verarbeitende 8-Bit-Worte werden in den temporären Registern a, b zwischengespeichert. Zu den Aufgaben der ALU gehört die Realisierung von Befehlen zur Addition, Subtraktion, logischen UND-, ODER-Verknüpfung, zum Größenvergleich, zum Erhöhen oder Erniedrigen von 8-Bit-Worten. Die arithmetisch-logische Einheit ist das Rechenwerk des Mikroprozessors.

Die <u>Bedingungs-Flip-Flops</u> (Flags, Zeichen) werden in Abhängigkeit vom Resultat der Verknüpfungsoperation der ALU gesetzt (Übertrag, Null, höchstwertigstes Bit, Parität). Sie gestatten Programmverzweigungen, Ruf-, Sprung- und Rücksprungoperationen.

Die Bedingungs-Flip-Flops (Flags) heißen:

- $C(\underline{carry}) = Ubertrag, Z(\underline{zero}) = Null,$

- $S(\underline{s}ign) = Vorzeichen, P(\underline{p}arity) = Parität.$

Ihre Zustände werden durch entsprechende Befehle ausgewertet.

wobei folgende Symbole als Bestandteile der Befehle festgelegt sind:

C für C = I (carry) bei Obertrag des Resultates

NC für C = O (no carry) kein Obertrag

Z für Z = I (zero) Resultat ist null

NZ für Z = 0 (no zero) Resultat ungleich null

M für S = I (minus) Resultat ist negativ.

P für S = 0 (plus) Resultat ist positiv

PE für P = I (parity even) Resultat ist gerade

PO für P = O (parity odd) Resultat ist ungerade

Die Bedingungs-Flip-Flope geben der Programmgestaltung eine große Flexibilität.

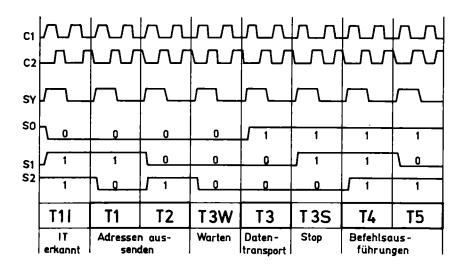

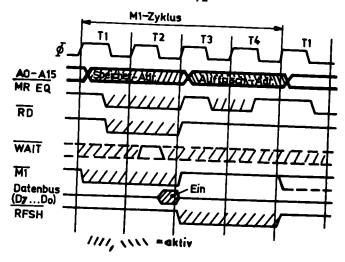

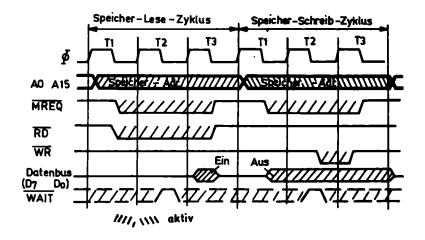

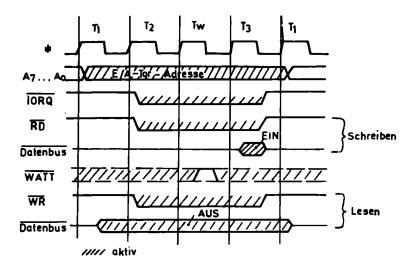

#### c) Zeit- und Ablaufsteuerung der CPU U808D

Die Abarbeitung eines Befehls des Mikroprozessors erfolgt in einem, zwei oder drei Maschinenzyklen (M-Zyklen). Jeder Maschinenzyklus wiederum zerfällt in Zeit-(Takt-)Zyklen (T-Zyklen) unterschiedlicher Länge. Der zeitliche Ablauf der Befehlsabarbeitung ist somit sowohl durch den aktuellen Befehl als auch durch die externen Steuersignale festgelegt. Als externe Steuersignale dienen immer die Signale C<sub>1</sub>, C<sub>2</sub> als Grundtakte und die Signale Interrupt IT (Unterbrechung) und Ready RD (Bereitschaft) als Modifikation der T-Zyklen-Anzahl. Hinzu kommt eine Beeinflussung des T-Zyklenablaufes beim Einschalten des Prozessors oder durch das Lesen eines Halt-Befehls, Bild 13 zeigt die Zeitsteuerung (T-Zyklen) des Prozessors U808D.

In den angegebenen 8 T-Zyklen vollziehen sich prinzipiell alle Operationen des Mikroprozessors sowohl innerhalb des Schaltkreises als auch extern in der Randelektronik. Eine aktive Funktion zur Befehlsabarbeitung haben jedoch nur die 5 Grundzyklen  $\rm T_1$  bis  $\rm T_5$ :

- T<sub>1</sub>: . Der Befehlszähler (PC) sendet den niederwertigen Teil seines Zählerstandes (8 Bit) aus: D<sub>7</sub>...D<sub>0</sub>, T<sub>1</sub>

- . Nach dem Aussenden wird der Befehlszählerstand automatisch um 1 erhöht.

- . Statusanzeige für  $T_1$ :  $S_2S_1S_0 = 010$

- T<sub>2</sub>: . Der Befehlszähler (PC) sendet den höherwertigen Teil seines Standes (6 Bit) aus: D<sub>5</sub>...D<sub>0</sub>, T<sub>2</sub>.

Niederwertiger und höherwertiger Teil bilden gemeinsem die Adresse (14 Bit): A<sub>13</sub>...A<sub>0</sub>.

Sie wird in einem externen Auffangregister (latch) zwischengespeichert, bis die Daten aus dem entsprechenden Speicherplatz gelesen sind.

- . Eine Erhöhung des Befehlszählerstandes des höherwertigen Teiles erfolgt aus dem Obertrag des niederwertigen Teils.

- . Die verbleibenden zwei Bit  ${\rm D_7D_6}$  des zweiten Taktes enthalten den Code für die Art des in Aberbeitung befindlichen Maschinenzyklus.

- . Statusanzeige für  $T_2$ :  $S_2S_1S_0 = 100$ .

- $T_3$ : . Nachdem mit  $T_1$  und  $T_2$  die Adresse eines Programmspeicherplatzes am Speicher anliegt, wird im Takt  $T_3$  der in diesem Platz befindliche Befehl gelesen (Befehlholen) und in das Befehleregister gebracht.

- . Ebenso werden im Takt T<sub>3</sub> Daten aus dem externen Speicher gelesen oder Daten in den externen Speicher geschrieben, wenn der enteprechende Maschinenzyklus vorliegt.

- . Statusanzeige für  $T_3$ :  $S_2S_1S_0 = 00I$

- $T_4$ , . Die Takte  $T_4$  und  $T_5$  dienen der Ausführung eines Befehls  $T_5$ : innerhalb der CPU (Rechenwerk und Registeroperationen)

- . Sind keine entsprechenden Operationen auszuführen, so werden diese Takte übersprungen.

- . Statusanzeige für  $T_4$ :  $S_2S_1S_0 = III$ ,  $T_5$ :  $S_2S_1S_0 = IOI$ .

Bild 13: Maschinenzyklus mit der maximal möglichen Anzahl von T-Zyklen

Diese 5 Grundtakte können modifiziert werden:

- $T_{11}$ : Am Ende eines jeden Befehles wird die Interrupt-Leitung abgefragt. Liegt eine Interrupt-Anmeldung vor, so ist IT = I. Dann wird ein internes Interrupt-FF gesetzt und anstelle des Zustandes  $T_1$  der Zustand  $T_{11}$  angenommen. Intern unterscheiden sich  $T_1$  und  $T_{11}$  nicht, jedoch wird nach außen zur Bestätigung der Interrupt-Anerkennung ein anderes Statussignal ausgesendet.

- . To folgt ohne Erhöhung des Befehlszählerstandes.

- . Statusanzeige für  $T_{11}$ :  $S_2S_1S_0 = IIO$ .

- $T_{3W}$ : . Ist am Ende des Zustandes  $T_2$  die Bereit-Leitung RD nicht I, d. h., es ist RD = 0, so muß die CPU mit der weiteren Befehlsabarbeitung warten, bis die Bereitschaft RD = I gemeldet wird. Erst dann geht  $T_{3W}$

in  $T_3$  über. Liegt RD stationär auf I, so wird  $T_{3W}$  übersprungen. Der Zustand  $T_{3W}$  kann ein beliebiges Vielfaches eines T-Zyklusses betragen. Die Däuer der Wartezeit der CPU hängt z. B. von den notwendigen Datenlesezeiten langsamerer externer Speicher ab. So kann grundsätzlich nach  $T_2$  ein  $T_{3W}$ -Zyklus folgen, um ein sicheres Datenlesen zu gewährleisten.

- . Statusanzeige für T<sub>3W</sub>: S<sub>2</sub>S<sub>1</sub>S<sub>0</sub> = 000.

- $\rm T_{3S}$ : . Wurde in  $\rm T_3$  ein programmierter oder über einen Eingabekanal anliegender Halt-Befehl gelesen, so geht die CPU in den  $\rm T_{3S}$ -Zustand (Stop).

- . Ebenso wird  $T_{\rm 3S}$  eingenommen, wenn die Betriebsspannung zugeschaltet wird.

- . Das Verlassen des Stop-Zustandes kann mit Hilfe eines kurzen Interrupt-Impulses (IT=I) ausgelöst werden.

- . Der Tag-Zuetand kann beliebig lange dauern.

- . Statusanzeige für  $T_{3S}$ :  $S_2S_1S_0 = OII$ .

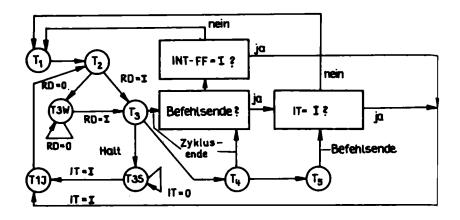

Das Zuetands-Flußdiagramm (Zuetandagraph) Bild 14 zeigt die möglichen Obergänge zwischen den T-Zuetänden. Die beeinflußbaren Bedingungen für den Obergang von einem T-Zustand in einen anderen sind an den Pfeilen oder in den Bedingungskästchen in der beschriebenen Weise angegeben. Das nach einer Interrupt-Erkennung gesetzte INT-FF bleibt so lange I, bis der Ein- oder Mehr-Byte-Interrupt-Befehl abgearbeitet ist, danach wird es automatisch rückgesetzt.

Unter Verwendung der Grund-T-Zyklen  $T_1$ ,  $T_2$ ,  $T_3$ ,  $T_4$ ,  $T_5$  kann der Mikroprozessor U8O8D folgende Maschinenzyklen (M-Zyklen) abarbeiten:

- PCI: . (<u>p</u>ut <u>c</u>ontrol <u>i</u>nstruction), Befehlsholezyklus. Jede Befehlsabarbeitung beginnt mit einem PCI-Zyklus, da sich alle Befehle im externen Programmspeicher oder in der Peripherie befinden.

- . M-Zyklus-Code für PCI:  $D_7D_6 = D0$ .

Bild 14 Zustandegraph zur Beschreibung der Obergänge zwiechen den T-Zuständen (S<sub>2</sub>,S<sub>1</sub>,S<sub>0</sub>)

- PCR: . (<u>put control read</u>), Speicherlese-Zyklus. Im Ergebnis des im PCI-Zyklus erkannten Befehls werden Daten vom Speicher in die CPU transportiert.

- . M-Zyklus-Code für PCR: D<sub>7</sub>D<sub>6</sub> = IO.

- PCW: . (<u>put control write</u>), Speicherschreib Zyklus. Entgegengesetzt zum Lese-Zyklus werden Daten in den externen Speicher geschrieben.

- . M-Zyklus-Code für PCW:  $D_7D_6 = II$

- PCC: . (<u>put control call</u>), Ein-, Ausgabe-Zyklus. Daten werden aus der Peripherie in die CPU oder von der CPU in die Peripherie transportiert.

- . M-Zyklus-Code für PCC: D<sub>7</sub>D<sub>6</sub> = OI.

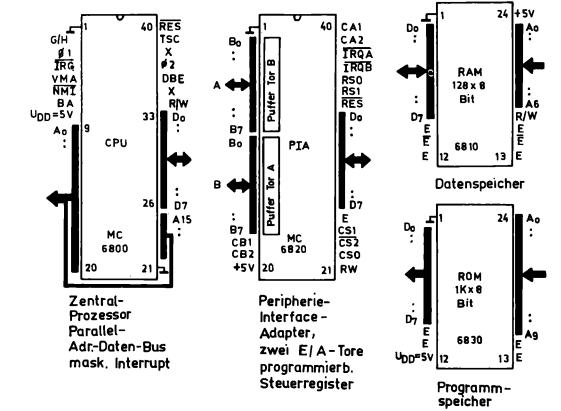

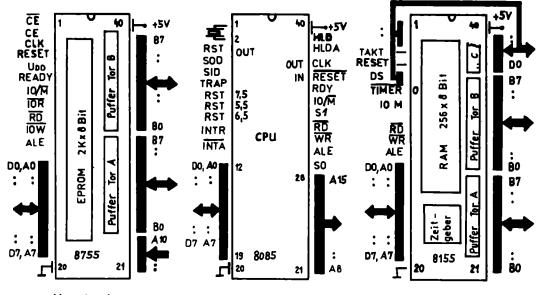

- d) Blockstruktur eines einfachen Mikrorechners mit der CPU U808D

Um den Mikroprozessor U808D in einem speziellen Gerät oder als Mikrorechner nutzen zu können, ist ein funktionsgerechter Aufbau vollständiger Baugruppen notwendig. Ein Anwendungsbeispiel ist in der Firmendokumentation des Kombinates Mikroelektronik beschrieben /91/.

Die im Bild 15 gezeigte Blockschaltung nach /91/ enthält folgende Funktionsgruppen:

- \_ CPU U808D als Mikroprozessor zur Befehlsabarbeitung und Zeitund Ablaufsteuerung.

- Taktgenerator für den nicht überlappenden Zweiphasentakt  ${\rm C_1}$ ,  ${\rm C_2}$  von z. B. 500 kHz.

- Bus-Treiber zur Stromverstärkung der Signale D. ... D.

- Auffang-Adreß-Register für die niederwertigen (8Bit)- und höherwertigen (6Bit)-Adreßteile der Takte T<sub>1</sub> und T<sub>2</sub> sowie für die zwei Bite D<sub>7</sub> D<sub>6</sub> zur M-Zyklus-Kodierung PCI, PCW, PCR, PCC.

- Adreßschalter zur Bildung der Gesamtadresse A<sub>13</sub>...A<sub>o</sub> und zur Blockauswahl der ROM- bzw. RAM-Speicherblöcke.

- Programm- und Datenspeicherblöcke (ROM, RAM).

- Ein-, Ausgabetore, die aus Puffer-Registern oder -Gattern gebildet werden und die Eingabe bzw. Ausgabe von Daten ermöglichen.

- E/A-Tor-Decoder zur Bildung der enteprechenden Tor-Adresse aus dem E/A-Adreßwort (RRMMM) und der E/A-Steuerung (I/O).

- Eingabe-Multiplexer zur Obernahme der Eingabe- und Speicher-Daten auf den bidirektionalen Bus der CPU.

- Steuer-Logik zur Verarbeitung externer Steuereignale wie Interrupt (IT), Bereitschaft (RD), der Statuseignale der T-Zyklen  $S_2S_1S_0$ , der Synchronisation  $S_y$ , der M-Zyklus-Kodierung  $D_7$   $D_6$  für PCI, PCR, PCW, PCC sowie der Ein-Ausgabe-Tor-Adreß-Bit-gruppe RR zur Ein-Ausgabesteuerung.

e) Befehle des Mikroprozessors U808D

# Befehlestruktur

Alle Befehle, Daten und Adressen sind aus 8-Bit-Worten der Form  $^{0}7^{0}6^{0}5^{0}4^{0}3^{0}2^{0}1^{0}$ o mit der Stellenwertigkeit  $^{0}n(^{0}n=2^{n})$  zusammengesetzt. Sie bestimmt den Maschinencode der Befehle. Befehlsstruktur:

. Ein-Wort-Befehle: Verwendung: Befehlscode Interner Register-D7D6D5D4D3D2D1D0 transfer, Operationen mit internen Registerdaten, Ein-/ Ausgabe-Operationen. Halt-, Rückkehr-/ und Verschiebe-Befehle. Memory-Operationen . Zwei-Wort-Befehle: Verwendung: 1. Wort D7D6D5D4D3D2D1D0 Befehlscode Operationen mit vorgegebenen Daten 2. Wort B7B6B5B4B3B2B1B0 Datenwort . Drei-Wort-Befehle: Verwendung: 1. Wort D<sub>7</sub>D<sub>6</sub>D<sub>5</sub>D<sub>4</sub>D<sub>3</sub>D<sub>2</sub>D<sub>1</sub>D<sub>0</sub> Befehlecode Ruf- und Sprung-Operationen 2. Wort A7A6A5A4A3A2A1A0 niederwertige 8 Bit d. Adreese 3. Wort X X  $^{A}_{13}^{A}_{12}^{A}_{11}^{A}_{10}^{A}_{9}^{A}_{8}$  höherwerti- ae 6 Bit ge 6 Bit

Die Bite  $\rm D_7$  und  $\rm D_6$  im 3. Wort ( $\rm A_{15}A_{14}$ ) werden von der CPU nicht bearbeitet und sind wahlfrei.

d. Adresse

Eine genaue Beschreibung der Basisbefehle ist in der Tabelle 1, Teile 1 bis 3, angegeben. Darin sind externe Speicherplätze (memory) durch M beschrieben, zu deren Adressierung die Inhalte der Register H und L verwendet werden.

Bei Register-Operationen ist für die Kodierung der Quellregister (source) SSS und der Senkenregister = Zielregister (drain) DDD. Im Binärcode ist für logisch "Eins" das Zeichen "I" verwendet. In den E/A-Befehlen beschreiben RR den Code der Torgruppen und

| Register-                  | Befehle     | Wirkung der Befehle               | Beschreibung der Befehle                               | Bemerkungen | Flage               |

|----------------------------|-------------|-----------------------------------|--------------------------------------------------------|-------------|---------------------|

| II DDD SSS                 | MOV, r1, r2 | (r1) <del>←</del> (r2)            | Lade Reg.r1 mit Inhalt Reg.r2                          |             |                     |

| II DDD III                 | MOV r,M     | (r) <b>←</b> (M)                  | Lade Reg.r mit Inhalt von M                            | (r2)=SSS    |                     |

| II III SSS                 | MOV M,r     | (M) <del>←</del> (r)              | Lade M mit Inhalt von Reg.r                            | -Quellreg.  |                     |

| 00 DDD IIO<br>87 BO        | MVI r       | (r) <del>←</del> B7B0             | Lade Register r mit den<br>Daten B7BO                  | (r1)=DDD    | ×                   |

| 00 III II0<br><b>B7</b> B0 | MVI M       | (M) <del>&lt;−−B</del> 7B0        | Lade Speicherplatz M mit den<br>Daten 8780             | -Zielreg.   |                     |

| 00 DDD 000                 | INR r       | (r)←(r)+1 (r≠A)                   | Erhöhe Inhalt von Reg.r um 1                           |             | Z,S,F               |

| 00 DDD 00I                 | DCR r       | (r) <del>&lt;</del> —(r)-1 (r≠A)  | Erniedr.Inh. von Reg.r um 1                            |             | Z,S,F               |

|                            |             |                                   |                                                        | r,r1,r2=    |                     |

| Akkumulator-               | Befehle     |                                   |                                                        | A 000       |                     |

| IO 000 SSS                 | ADD r       | (A) <b>←</b> (A)+(Γ)              | Addiere den Inhalt von:r,                              | B 001       |                     |

| 10 000 111                 | ADD M       | (A) <del>←</del> (A)+(M)          | м                                                      | C 010       |                     |

| 00 000 I00<br>B7 B0        | ADI         | (A) <del>←</del> (A)+B7B0         | bzw.die Daten B7BO zum<br>Akku-Inhalt,Resultat im Akku | D 011       | ,                   |

| IO 001 SSS                 | ADC r       | $(A) \leftarrow (A) + (r) + (Cy)$ | Add. Inhalt von: r und Cy,                             | H IOI       | ٠.                  |

| 10 001 111                 | ADC M       | $(A) \leftarrow (A) + (M) + (Cy)$ | M und Cy                                               | L IIO       | 811<br>2,5          |

| 00 00I I00<br>B7 B0        | ACI         | (A) ← (A)+B7B0+(Cy)               | bzw.die Daten B7BO u. Cy<br>zum Akku,Resultat im Akku  | M III       | tzt (               |

| 10 010 SSS                 | SUB r       | (A) <del>←</del> (A)-(r)          | Subtrahiere Inhalt v.: r,                              | Adressier.  | 80 B                |

| 10 010 111                 | SUB M       | (A) <del>-</del> (A)-(M)          | м                                                      | von M       | 9 t                 |

| 00 0I0 I00<br>B7 B0        | SUI         | (A) <del></del>                   | bzw.die Daten B7BO zum<br>Akku-Inhalt,Resultat im Akku | durch HL;   | Resulte<br>ingunge- |

| IO OII SSS                 | SBB r       | $(A) \leftarrow (A) - (CY)$       | Sub.Inhalt von: r und Cy                               | Cy=Carry    | Rei                 |

| 10 011 111                 | SBB M       | $(A) \leftarrow (A) - (M) - (Cy)$ | M und Cy                                               | entspr.dem  | 8 8                 |

| 00 0II 100<br>B7 B0        | SBI         | (A) - (A) - B7B0-(Cy)             | bzw.die Daten 87BO u.Cy<br>zum Akku,Resultat im Akku   | Flag:C      | 0 6                 |

| Akkumulator-6          | Befehle | Wirkung der Befehle                     | Beschreibung der Befehle                                | Bemerkungen                  | Flags             |

|------------------------|---------|-----------------------------------------|---------------------------------------------------------|------------------------------|-------------------|

| 10 100 SSS A           | NA r    | (A) <b>←</b> (A)∧ (r)                   | Bilde das logische UND von: r                           |                              |                   |

| IO IOO III AN          | NA M    | (A) <del>←</del> (A) ∧ (M)              | M                                                       |                              | ٥,                |

| 00 100 100 AM<br>B7 BO | NI      | (A) <b>←</b> (A) <b>∧</b> B7B0          | bzw. den Daten B7BO mit<br>dem Akku-Inhalt,Res. im Akku |                              | 2,5               |

| IO IOI SSS XF          | RA r    | (A) <del></del> (A) <del>∀</del> (r)    | Bilde EXCLUSIV-ODER von: r,                             | EXCL.ODER                    |                   |

| IO IOI III XF          | RA M    | (A) <b>←</b> (A) <b>∀</b> (M)           | М                                                       | entspricht                   | zt                |

| 00 IOI IOO XF<br>B7 BO | RI      | (A) <b>→</b> (A) <b>∀</b> B7B0          | bzw.den Daten 8730 mit<br>dem Akku-Inhalt,Res.im Akku   | Antivalenz                   | set<br>0          |

| IO IIO SSS OF          | RAr     | (A) <b>←</b> (A) <b>∨</b> (r)           | Bilde INCLUSIV-ODER von: r                              |                              | tat<br>Cy=        |

| 10 110 111 Of          | RA M    | (A) • (A) V (M)                         | М                                                       | i                            | ul<br>r           |

| 00 IIO IOO OF<br>B7 BO | RI      | (A) <b>←</b> (A) <b>V</b> B7B0          | bzw.den Daten B7BO mit<br>dem Akku-Inhalt,Res. im Akku  |                              | Res<br>abe        |

| IO III SSS CN          | MP r    | (A) - (r)                               | Vergleiche Inhalt von: r,                               | (r),(A),(M)                  | 118<br>:<br>P     |

| IO III III C           | MP M    | (A) - (M)                               | м                                                       | u.D7D0                       | ebn<br>zt:<br>,S, |

| 00 III 100 CF<br>B7 B0 | PI      | (A) - B7BO                              | bzw.die Daten B7BO mit<br>Akku-Inhalt                   | bleiben<br>unverän <b>d.</b> | Erg<br>set<br>C,Z |

| 00 000 010 RL          | LC      | Cy+B7+B0+                               | Verschiebe Akku- ( links                                |                              |                   |

| 00 00I 0IO R           | RC      | B7-B0 -Cy                               | Inhalt nach: rechts                                     |                              | is<br>C           |

| 00 010 010 RA          | AL      | <u>Cy</u> + <u>6</u> 7 <del>4</del> −80 | Verschiebe Akku- (links                                 |                              | ebn<br>zt:        |

| 00 0II 0I0 RA          | AR      | •B7—B0 <b>→</b> Cy                      | Inhalt durch den Chechts Übertrag nach:                 |                              | Erge<br>setz      |

| Ein-Ausgab | e-Befehl | 9                        |                              |             |           |